Other Parts Discussed in Thread: TLK10232, TM4C129DNCPDT

Hi

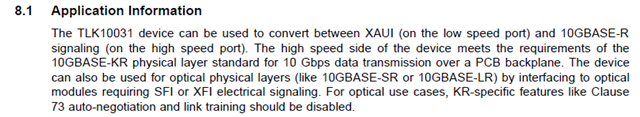

We are implementing 10G repeater application using 2 number of TLK10031 PHY transceivers.

Please find the attached block diagram for the application.

As per application we should connect HS to TLK10031 High side (chip 1) , CHIP 1 it should convert to low side of and to be connected to low side of TLK10031 chip 2 & from the HS of TLK10031 (chip 2) we shall receive the 10 G regenerated signal.

While testing, we are applying 10G signal from external source to TLK10031 High side (chip 1) but we are not getting any HS signal at chip 2.

While testing we have checked the values of following pins.

PDTRXA_N (Pin A8) : HIGH

PRBSEN (Pin B9) : HIGH

ST, MODE_SEL (Pin M9, H10) : LOW, LOW as per mentioned in datasheet.

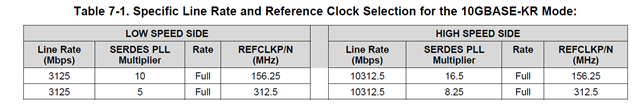

We are providing input clock : 156.25Mhz

But we are not able get the output.

LOS_A (Pin E9) , PBRS_PASS (PIn J9) are continously low.

Please support us