- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

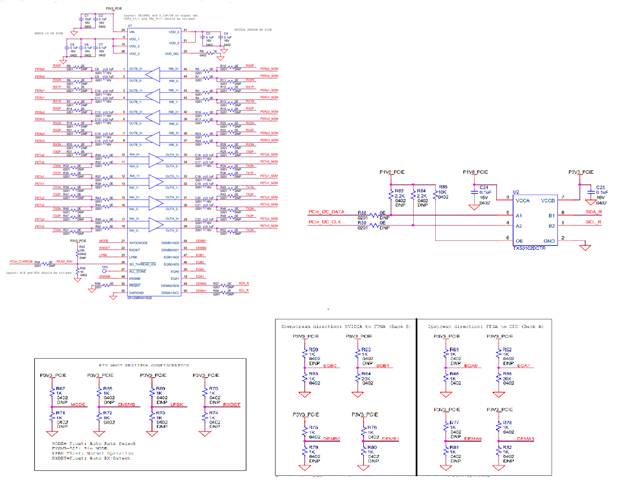

In our design, we have used Jetson NX as Root Complex and Arria 10 FPGA SoC board as End Point configuration.

Due to long PCIe traces + cable length in between those two boards (~15-20"), we have used redriver IC# DS125BR401SQE for the signal integrity and stable PCIE operation.

Initially, we have configured redriver IC as hardware bootstrap mode (Pin Mode), but during bring-up we have found that PCIE link training is not getting up, link isn't up.

So, we have bypass redriver IC, and PCIE link training getting successful and link is getting up, but data communication couldn't be done between two board.

Now, we are planning to change Pin Mode to SMBus configuration of redriver IC for detailed analysis and register debugging of the redriver IC.

We have attached snapshot of the our schematic design for your reference, please review it and it would be great for us if you can suggest any improvement points for the same.

Also, please share the Linux SMBus driver or application of part# DS125BR401SQE for the software debugging.

Kindly let me know if you need more details on it.

Regards,

Pinkesh Vaghela

Hi Pinkesh,

Here are a couple notes based on your schematic:

After switching to SMBus mode, I would recommend starting with a lower equalization setting than you need and work your way up to higher equalization settings. Is it possible for you to share any eye diagrams at different points in the link?

Regarding device configuration, we don't have a linux specific driver for this part. You can use the i2cget / i2cset commands to read/write the device. You could also use sigcon architect with a DS125BR401 profile and a USB2ANY device in order to configure the part via a GUI.

https://www.ti.com/tool/SIGCONARCHITECT

https://www.ti.com/tool/USB2ANY

Thanks,

Drew