Part Number: DS125BR401

Other Parts Discussed in Thread: DS100KR401

Tool/software:

Hi Team,

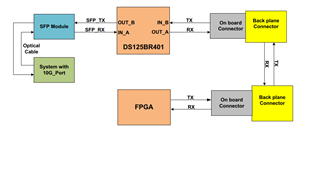

We are using DS125BR401SQE/NOPB in our design for 10G Ethernet links (Do not require link training ) from FPGA to SFP+ interface through back plane connections. We set the redriver in limiting mode by connecting mode pin with pull down resistor to GND.

During 10G Link validation test we observed that out link is getting up, But it creating errors randomly. We tried to optimize the link setting (VOD,EQ,DEM) of DS125BR401S, but still we can not achieve the error free channels.

We configured SD_TH in high state and we set the below mentioned signal detect registers for forcing forcing the Signal Detect function to be always ON.

0x0D[1]= 1'b, 0x14[1] = 1'b, 0x1B[1] = 1'b, 0x22[1] = 1'b

0x2A[1]= 1'b, 0x31[1] = 1'b, 0x38[1] = 1'b, 0x3F[1] = 1'b

Observation 1:

We can able to achieve the error free channel while we set redriver during INB to OUTA loop back mode by writing 21 value in 0x02 register.

We attached the current redriver register value for your reference. Refer attached image for loop back scheme diagram.

After validating back plane level loop back testing, we set 31 value in 0x02 register for normal operation in that case our link itself not active. So we programmed 50 value in 0x08 register & 20 value in register (0E,15,1C,23,2B,32,39 & 40) for idle control from registers to set output ON function.

In this case 10G link up but still we have random error.

Question 1: Can you please suggest what is the suggested setting for 10GbE interface in optical link(With out Auto Negotiation)?

Question 2: In 9.5.1.1.1 section of DS125BR401 data sheet mentioned that “This data loss can be eliminated by disabling automatic detection and forcing the Signal Detect function to be always ON”

How to disable the automatic detection in DS125BR401?

What are register I need to overwrite for this operation?

Thanks in advance,

Esakki.