Other Parts Discussed in Thread: ALP

Hi team,

One of our customers' questions are as follows

1. Problem background:

At present, Qualcomm platform is used to output DSI image data, and then a bridge chip is used to convert DSI to CSI signal to obtain CSI signal.

Then use DS90UB953+DS90UB960 to transmit the CSI signal to another platform through FPD-LINK for reception. The platform will preview the CSI output signal of 960 directly as camera data.

2. Current issues:

When the receiving platform previews the data, it is found that the picture is shaking, and it looks like some pixels are slightly jumping horizontally.

3. Direction checked:

Configure the bridge chip to the pattern output mode. In this case, the preview screen is still shaking.

Configure DS90UB953 to pattern output mode. In this case, the preview screen will no longer shake.

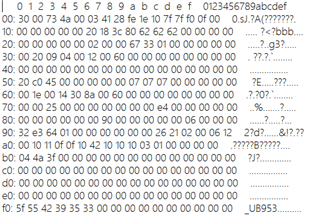

From the above experiments, we think that there may be a problem with the 953 state, resulting in shake, but we are not sure how to troubleshoot it. When the problem occurs, we dump the 953 register. The results are as follows. Please help confirm the 953 state.

Best Regards,

Amy Luo