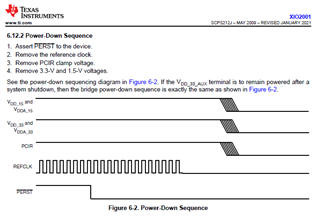

From the datasheet the power down sequence is defined as below. There are no timing elements defined as per the power-up sequence.

Is it necessary that the REFCLK is stopped before the PCIR and Power rails are removed? Is there a time that the clock must be inactive before the voltages are removed.