Hi,

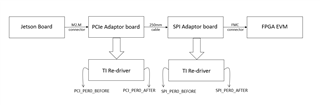

In our design, we have used Jetson NX as Root Complex and Arria 10 FPGA SoC board as End Point configuration.

Hardware configurations (boot strapping) for, PCIe generation 2, x2 (lane 0 and lane1), the repeater is as follow,

Equalization=0x02, for FR4 10-inch trace,

De-emphasis=-3.5dB,

VOD=0.9V.

Link is stable and communication between boards is working fine.

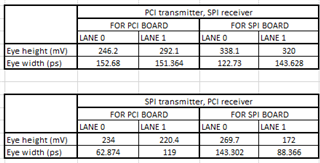

Results captured before and after repeater IC for lane 0, where Jetson kit is transmitting and FPGA is receiving, as per bring-up test are as follow

On PCI board, before repeater IC:

On PCI board, after repeater IC:

On SPI board, before repeater IC:

On SPI board, after repeater IC:

We’re getting similar results when communication is inversed and on lane 1 as well in both situations.

I wanted to know that if eye-diagram captured are as expected or not, and why eye is bulged after, and it is more accurate before repeater. If yes, what is the technical reason behind such behaviour?

Moreover, as you can see in block diagram we have two adaptor boards, PCIe and SPI, and we’re not getting same type of eye behaviour at, after repeater on PCIe board and before repeater on SPI board.

Thanks,

Zeel Shah