Other Parts Discussed in Thread: ALP

Hello,

LCD resolution is 1920x720@ 60,DS90UB947 connected to Soc with Dual Link , UB948 is soldered on TFT board on which there is one MCU. And the timing and register configuration of the UB948 is configured by the MCU on the TFT board.

LOCK pin of UB948 is always high when the problem appeared. PCLK is stable which is output os Soc, and the display is still flower screen after plugging in the FPD-LINKIII twisted pair. The probability is very low, with thousands of units produced and a few.

mode_SEL hardware configuration is as follows (the software does not have the 0x4f register):

:

:

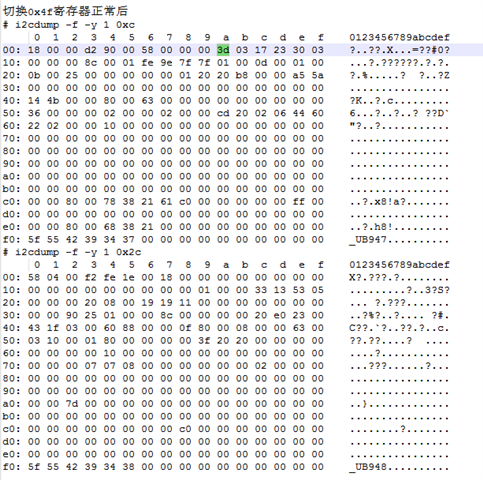

This is the register value for 947 and 948 when the screen is floral (above figure), and several CRC counts that appear are abnormal, such as the following figure 0xa = 0x3b, 0xb = 0x2, 0xc = 0x17.

In addition, he also used the no flower screened environment to verify -- "Configuration 0x04 clears CRC error, then reads these registers to see if the error is still reported" However, the device did not restart modifying 0x4f register is 0xc0 and then changing back to 0x0. Read register (figure below) 0xa = 0x3d, 0xb = 0x3,0xc= 0x17.

It looks like the CRC count has increased significantly. I tried the normal situation, register value 0xa = 0x3, 0xb =0x0,0xc= 0x07. Modify the 0x4f = 0xc0 and then change back to 0x0. 0xa= 0xf, 0xb=0x0,0xc= 0x07. The count only increased by 12.

Best regards

Kailyn