Part Number: SN65DP141

hi expert,

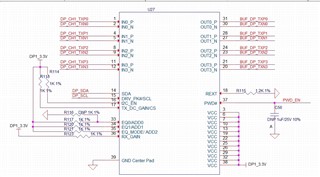

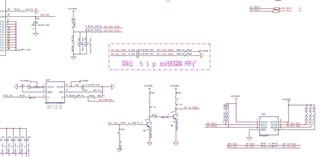

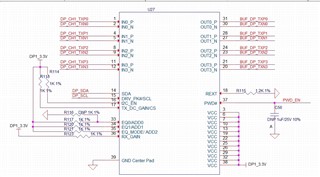

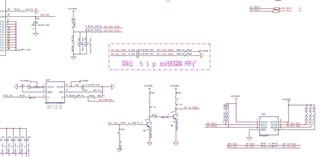

Could you help check the schematics of SN65DP141,Now our products are always showing flower screens!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN65DP141

hi expert,

Could you help check the schematics of SN65DP141,Now our products are always showing flower screens!

Hi,

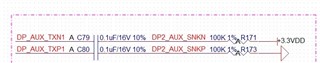

Are you AC coupling the AUX signal and having 100k pullup to 3.3V on AUXN and 100k pulldown on AUXP?

Are you also configuring DP141 through its registers?

I assume both the DP141 input and the output are AC coupled? The flower picture should come from the DP source, the DP141 will not generate any pattern since it is a re-driver only.

Thanks

David

hi David,

Ac coupled AUX signals, 100k pull-up to 3.3V on AUXN, 100k pull-down on AUXP, are available.

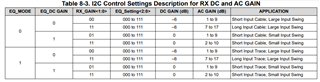

The software is configured with DP141 through its registers. The four registers configured are as follows, and the configured values are as follows;

registers data

0x02 0x03

0x05 0x06

0x08 0x06

0x0B 0x06

Hi,

Is there a reason you are programming lane 0 with a different value than the other three lanes?

I assume this is a source side design, how long is the trace from the DP source to DP141? Have you done the DP compliance testing?

Refer to the table below, it looks like you are doing cable mode, is this correct?

Thanks

David

Hi,

Can you share your layout? How long is the trace length from the DP source to the DP141?

Have you done the DP compliance test yet?

Can you also share a picture of your flower screen?

Thanks

David

hi

It is not convenient to share layout

5860mil from DP source to DP141; configuration:cable mode ,

What is the DP compliance test?

Whether there is a recommended solution for DP141 output protection?

Hi,

Does the 5860mil include the cable or just the trace length? What data rate are you running, 2.7G, 5.4G, or 8.1G?

I would disable DRV_PEAK for now, so register 0x03, 0x06, 0x09, 0x0C would be set to 0x00, and I would change the EQ setting (bit 6-4) of register 0x02, 0x05, 0x08, and 0x0B to see if it improves the flicking screen would improve, you can start with a value of 0x38.

Thanks

David

hi expert,

I changed the value of the register, but there is no improvement, do you have a better way for this?

Hi,

Can you please accept my friendship request so you can send me the schematic and layout (Allegro format) in a private message?

Have you tried to change to a shorter cable and see it helps?

If you go with a lower video resolution, does it help as well?

Thanks

David