Part Number: TCAN4550

Hi Team,

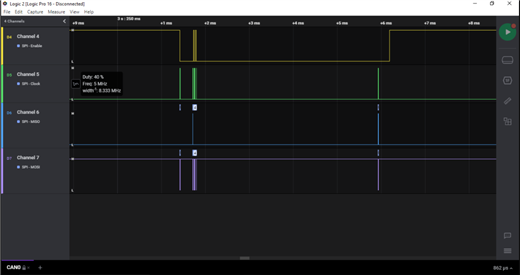

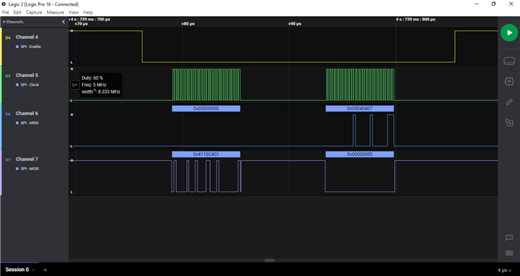

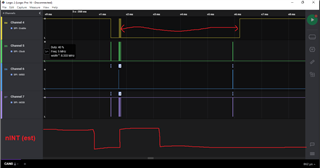

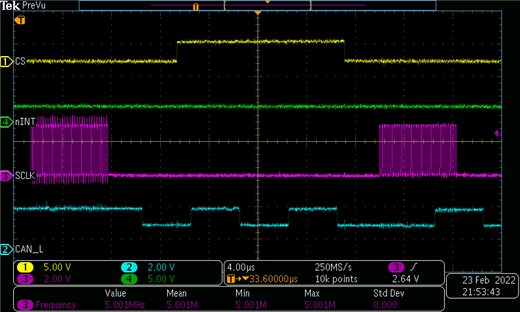

As I am using tcan4x5x driver, I am executing send cansend data continuously. When data is sent the values of RX bytes in ifconfig is incrementing accordingly. For some amount of time, the RX packets increment stops and no more data is able to receive and send. At this moment, no error messages from the driver.

$ ifconfig

can0 Link encap:UNSPEC HWaddr 00-00-00-00-00-00-00-00-00-00-00-00-00-00-00-00

UP RUNNING NOARP MTU:16 Metric:1

RX packets:65212 errors:0 dropped:0 overruns:0 frame:0

TX packets:65213 errors:0 dropped:2 overruns:0 carrier:2

collisions:0 txqueuelen:10

RX bytes:521696 (509.4 KiB) TX bytes:521704 (509.4 KiB)

Interrupt:72

When I run "ifconfig can0 down" and send cansend (after can initialisation) commands, the RX packets starts incrementing and stops after some amount of time.

Please help me to solve this problem.

Best regards,

AyshaT