Dear TI team:

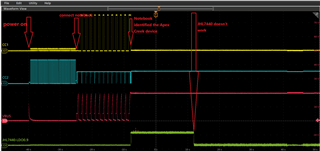

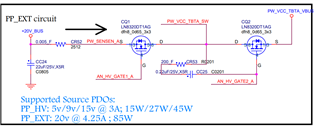

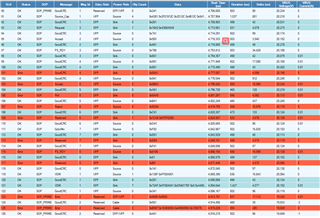

We are currently developing a TBT3 Titan-Ridge DD project, and the PD chip used is TPS95683B used on the reference version. I am not sure about the configuration of FW. Attached is our schematic diagram for your reference.

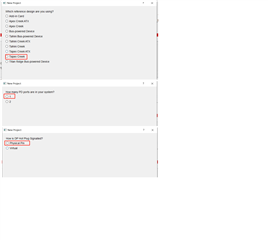

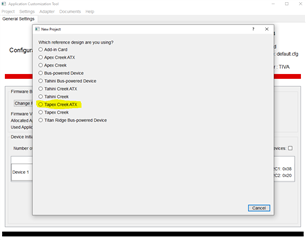

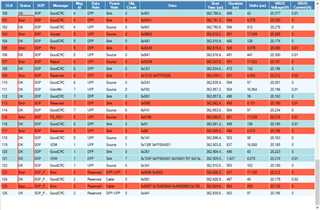

We need type-c to output 5V@3A,9V@3A,15V@3A,20V@3.25A through ATX power supply, but could you please help to confirm the specific FW configuration? The attached screenshot shows the FW configuration.

Tanks!