- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear Team,

Our customer are using the SN65DSI84 LVDS bridge for our LCM project.

LCM might show black screen while turning on or off screen.

Action of turning on or off screen is including turn on DSI relative from SOC and re-intilalize SN65DSI84.

Is re-initializing SN65DSI84 must if we don't need to take care of power consumption?

Can we just turn off the DSI relative thing only and don't change anything of bridge?

Many Thanks,

Jimmy

Jimmy

Are you putting the SOC into ULPS state?

Once the SOC is enabled, You may need to wait for a minimum of 3 ms. and then set the DSI94 SOFT_RESET bit (CSR 0x09.0).

Thanks

David

Hi David,

Thanks for your support!

Do our customer have to set "DSI94 SOFT_RESET" while SOC leaves ULPS?

There's a 3% failure rate with "soft_reset" while SOC leaves ULPS(system resume).

There's almost 0 failure rate without "soft_reset" while SOC leaves ULPS.

Do our customer need some actions for sn65dsi84 while SOC leaves ULPS? (seems to work well if we do nothing about the bridge.)

Many Thanks,

Jimmy

Jimmy

The SOFT_RESET bit must be set after making any changes to the DIS clock rate or after changing between DSI burst and non-burst modes. For when the SOC enters and leaves ULPS, are they changing the DSI clock? Can they probe the clock using a scope?

So if they remove setting of the SOFT_RESET bit, then the issue is resolved?

Thanks

David

Hi David,

We appreciated your great support!

The DSI (MIPI) paths are in the inner layer for good impedence and EMI so can't probe it. Is there any other way to check it? Please review the schematics as well again. Thanks a lot!

Jimmy

Jimmy

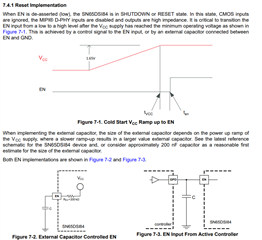

I noticed that they are driving the DSI84 EN pin externally. In this case, are they meeting the DSI84 power up timing requirement as listed below?

What happens if they change to the passive RESET timing as shown in Figure 7-2?

Also, if they remove setting of the SOFT_RESET bit, then the issue is resolved?

Thanks

David