Other Parts Discussed in Thread: SN65DSI84,

Hi team,

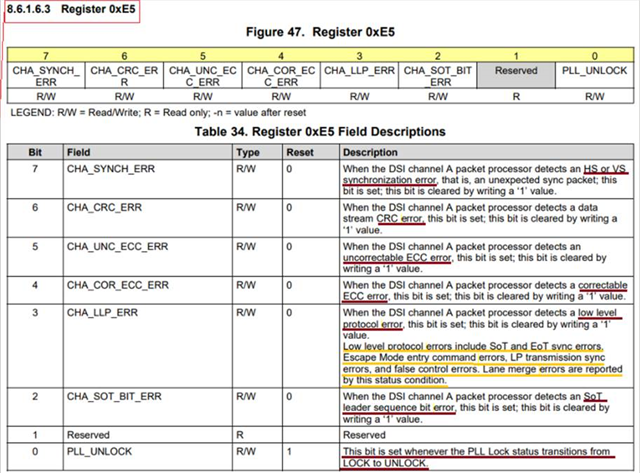

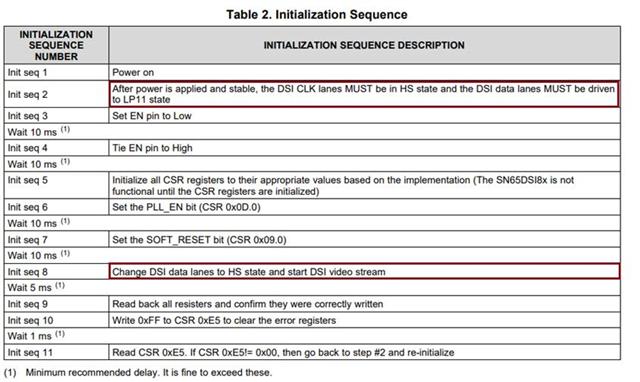

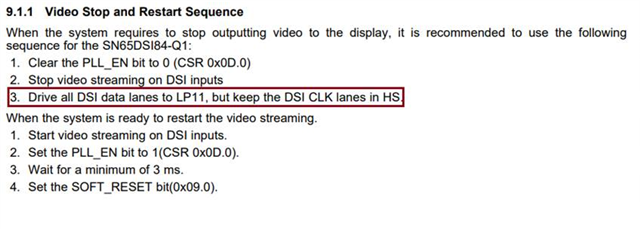

We’ve few queries w.r.t recovery after link-loss detection (0xE5)

1. What recovery mechanism we’re going to implement for each error that’s corresponds to each bit in below registers.

2. With respect to correctable ECC and CRC error, is the bridge chip sn65dsi84 capable of handling it on its own without the intervention of software? (Chip level recovery).