Hello,

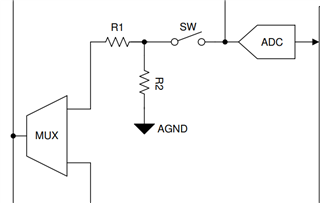

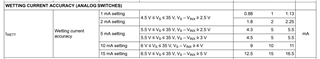

I'm trying to work in ADC mode and I know ADC range is upto 6V. I saw a resistor divider in front of ADC in functional block diagram where i do not know its values. So What is the voltage range i can give to IN0 pin to get the ADC output without saturation?