Other Parts Discussed in Thread: SN65DSI83

Hello team,

My customer use SOC-->SN65DSI83-->DS90UB927-->DS90UB928(display module) in their application.

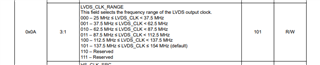

Display company met flicker issue and insisted root cause is H-blank has variation at 928 LVDS output.

but 927/928 device use internal PCLK and sync with output so that this doesn't have variation.

So my customer question if SN65DSI83 device can generate Hblanking parameter variation a little.

Could you pls help me answer this to customer??

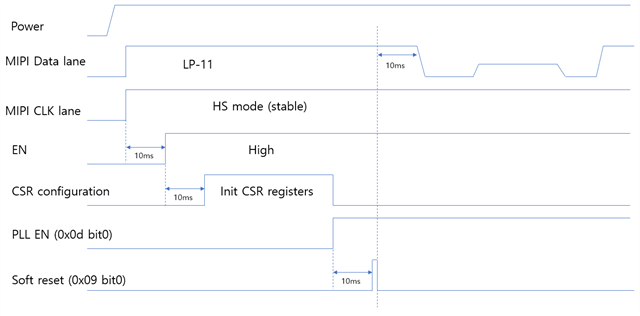

Attached is DSI tuner setting and timing info.

Thank you.