Our setup for the TLK10031 is

Ref clock = 156.25MHz

- LS side: connected to 4 channels XAUI

HS side: connected to Xilinx FPGA via backplane.

Please advise how to configure TLK10031 to 10-KR mode with Auto Negotiation disable.

Thank you,

Moshe

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Our setup for the TLK10031 is

Ref clock = 156.25MHz

- LS side: connected to 4 channels XAUI

HS side: connected to Xilinx FPGA via backplane.

Please advise how to configure TLK10031 to 10-KR mode with Auto Negotiation disable.

Thank you,

Moshe

See attached configuration script for reference.

//******************************************************************************************** // // Copyright Texas Instruments Inc // TI Proprietary Information Internal Data // This is a general provisioning script for the TLK10034 10GKR Mode Apply Settings Portion of the GUI // When using Auto Negotiation. // This script sets the bits in Register VS_SERDES_CFG_OVERRIDE_CTRL (1E.8020.9:0) to "0x0200". // The bits in Register AUTO_CLKOUT_CONTROL (1E.8021) are set to the value of "0x006F" // The KR_FEC_ERR_IND_EN and KR_FEC_EN bits in Register KR_FEC_CONTROL (01.00AB.1:0) are set to 2'b00. // // Author: Jonathan Nerger // Modified Date: April 23, 2012 // Revision: Rev 0.1 //******************************************************************************************** //******************************************************************************************** // Script Command Parameter Reference //******************************************************************************************** //SET BOARD(BOARD_NUMBER) //MDIO45 WRITE (CHANNEL_NAME,®ISTERNAME) //MDIO45 WRITE IMM (CH_ADDR,DEVICE_ADDR,REGISTER_ADDR,REGISTER_VALUE) //MDIO45 READ (CHANNEL_NAME,®ISTERNAME) //MDIO45 READ UNTIL (CHANNEL_NAME,®ISTERNAME,MASK,EXPECTED,TIMEOUT(ms)) //MDIO45 READ IMM(CH_ADDR,DEVICE_ADDR,REGISTER_ADDR,MASK,EXPECTED,TIMEOUT(ms)) //I2C WRITE (®ISTER_NAME) //I2C WRITE IMM (DEVICE_ADDRESS,REGISTER_ADDRESS, REGISTER_VALUE ) //I2C READ (®ISTER_NAME) //I2C READ UNTIL (®ISTER_NAME, MASK, EXPECTED,TIMEOUT(ms)) //I2C READ IMM (DEVICE_ADDRESS,REGISTER_ADDRESS, MASK, EXPECTED,TIMEOUT(ms)) //DELAY (This reads the test time per parameter field in the HS Link Optimizer and waits that amount of time) //WAIT(time ms) //MDIO45 WRITE FUNC (CHANNEL_NAME, FIELD_NAME, Data[in hex]) //******************************************************************************************** // Soft Reset and Mode Configuration //******************************************************************************************** // Configure MODE_SEL and ST Pins I2C WRITE (REGISTER_05) // Wait 100mS WAIT(100) // Soft Reset & disable global config //MDIO45 WRITE IMM (0x0,0x1E,0x0000,0x8000) MDIO45 WRITE FUNC (GLOBAL,GLOBAL_RESET,0x1) MDIO45 WRITE (GLOBAL,GLOBAL_CONTROL_1) // Configure Operating Mode Registers MDIO45 WRITE (A,CHANNEL_CONTROL_1) MDIO45 WRITE (A,AN_CONTROL) MDIO45 WRITE (B,CHANNEL_CONTROL_1) MDIO45 WRITE (B,AN_CONTROL) MDIO45 WRITE (C,CHANNEL_CONTROL_1) MDIO45 WRITE (C,AN_CONTROL) MDIO45 WRITE (D,CHANNEL_CONTROL_1) MDIO45 WRITE (D,AN_CONTROL) //******************************************************************************************** // CH A Provisioning //******************************************************************************************** MDIO45 WRITE (A,CHANNEL_CONTROL_1) MDIO45 WRITE (A,HS_SERDES_CONTROL_1) MDIO45 WRITE (A,HS_SERDES_CONTROL_2) MDIO45 WRITE (A,HS_SERDES_CONTROL_3) MDIO45 WRITE (A,HS_SERDES_CONTROL_4) MDIO45 WRITE (A,LS_SERDES_CONTROL_1) MDIO45 WRITE (A,LN3_LS_SERDES_CONTROL_2) MDIO45 WRITE (A,LN2_LS_SERDES_CONTROL_2) MDIO45 WRITE (A,LN1_LS_SERDES_CONTROL_2) MDIO45 WRITE (A,LN0_LS_SERDES_CONTROL_2) MDIO45 WRITE (A,LN3_LS_SERDES_CONTROL_3) MDIO45 WRITE (A,LN2_LS_SERDES_CONTROL_3) MDIO45 WRITE (A,LN1_LS_SERDES_CONTROL_3) MDIO45 WRITE (A,LN0_LS_SERDES_CONTROL_3) MDIO45 WRITE (A,HS_OVERLAY_CONTROL) MDIO45 WRITE (A,LS_OVERLAY_CONTROL) MDIO45 WRITE (A,LOOPBACK_TP_CONTROL) MDIO45 WRITE (A,LS_CONFIG_CONTROL) MDIO45 WRITE (A,LN3_LS_CH_CONTROL_1) MDIO45 WRITE (A,LN2_LS_CH_CONTROL_1) MDIO45 WRITE (A,LN1_LS_CH_CONTROL_1) MDIO45 WRITE (A,LN0_LS_CH_CONTROL_1) MDIO45 WRITE (A,HS_CH_CONTROL_1) //MDIO45 WRITE IMM (0x0,0x1E,0x8020,0x0200) MDIO45 WRITE (A,VS_SERDES_CFG_OVERRIDE_CTRL) MDIO45 WRITE FUNC (A,LS_PLL_MULT_OVERRIDE,0x0) MDIO45 WRITE FUNC (A,LS_RATE_OVERRIDE,0x0) MDIO45 WRITE FUNC (A,HS_PLL_MULT_OVERRIDE,0x0) MDIO45 WRITE FUNC (A,HS_RATE_OVERRIDE,0x0) MDIO45 WRITE FUNC (A,HS_FIRUPT_OVERRIDE,0x1) MDIO45 WRITE FUNC (A,HS_ENRX_OVERRIDE,0x0) MDIO45 WRITE FUNC (A,HS_AZCAL_OVERRIDE,0x0) MDIO45 WRITE FUNC (A,HS_ENTRACK_OVERRIDE,0x0) MDIO45 WRITE FUNC (A,HS_EQHLD_OVERRIDE,0x0) MDIO45 WRITE FUNC (A,HS_TWCRF_OVERRIDE,0x0) MDIO45 WRITE FUNC (A,HS_TWPOST2_OVERRIDE,0x0) MDIO45 WRITE FUNC (A,HS_TWPOST_OVERRIDE,0x0) MDIO45 WRITE FUNC (A,HS_TWPRE_OVERRIDE,0x0) MDIO45 WRITE FUNC (A,HS_SWING_OVERRIDE,0x0) //MDIO45 WRITE IMM (0x0,0x1E,0x8021,0x006F) MDIO45 WRITE (A,AUTO_CLKOUT_CONTROL) MDIO45 WRITE FUNC (A,HS_PLL_LOCK_CHECK_DISABLE,0x1) MDIO45 WRITE FUNC (A,HS_LOS_CHECK_DISABLE,0x1) MDIO45 WRITE FUNC (A,SYNC_STATUS_CHECK_DISABLE,0x0) MDIO45 WRITE (A,PMA_CONTROL_1) MDIO45 WRITE (A,KR_TRAIN_CONTROL) MDIO45 WRITE (A,KR_FEC_CONTROL) MDIO45 WRITE FUNC (A,KR_FEC_ERR_IND_EN,0x0) MDIO45 WRITE FUNC (A,KR_FEC_EN,0x0) MDIO45 WRITE (A,KR_VS_FIFO_CONTROL_1) MDIO45 WRITE (A,KR_VS_TP_GEN_CONTROL) MDIO45 WRITE (A,KR_VS_TP_VER_CONTROL) MDIO45 WRITE (A,KR_VS_CTC_ERR_CODE_LN0) MDIO45 WRITE (A,KR_VS_CTC_ERR_CODE_LN1) MDIO45 WRITE (A,KR_VS_CTC_ERR_CODE_LN2) MDIO45 WRITE (A,KR_VS_CTC_ERR_CODE_LN3) MDIO45 WRITE (A,PCS_CONTROL) MDIO45 WRITE (A,PCS_TP_SEED_A0) MDIO45 WRITE (A,PCS_TP_SEED_A1) MDIO45 WRITE (A,PCS_TP_SEED_A2) MDIO45 WRITE (A,PCS_TP_SEED_A3) MDIO45 WRITE (A,PCS_TP_SEED_B0) MDIO45 WRITE (A,PCS_TP_SEED_B1) MDIO45 WRITE (A,PCS_TP_SEED_B2) MDIO45 WRITE (A,PCS_TP_SEED_B3) MDIO45 WRITE (A,PCS_TP_CONTROL) MDIO45 WRITE (A,PCS_VS_CONTROL) MDIO45 WRITE (A,AN_CONTROL) MDIO45 WRITE (A,AN_ADVERTISEMENT_1) MDIO45 WRITE (A,AN_ADVERTISEMENT_2) MDIO45 WRITE (A,AN_ADVERTISEMENT_3) MDIO45 WRITE (A,AN_XNP_TRANSMIT_1) MDIO45 WRITE (A,AN_XNP_TRANSMIT_2) MDIO45 WRITE (A,AN_XNP_TRANSMIT_3) //******************************************************************************************** // CH B Provisioning //******************************************************************************************** MDIO45 WRITE (B,CHANNEL_CONTROL_1) MDIO45 WRITE (B,HS_SERDES_CONTROL_1) MDIO45 WRITE (B,HS_SERDES_CONTROL_2) MDIO45 WRITE (B,HS_SERDES_CONTROL_3) MDIO45 WRITE (B,HS_SERDES_CONTROL_4) MDIO45 WRITE (B,LS_SERDES_CONTROL_1) MDIO45 WRITE (B,LN3_LS_SERDES_CONTROL_2) MDIO45 WRITE (B,LN2_LS_SERDES_CONTROL_2) MDIO45 WRITE (B,LN1_LS_SERDES_CONTROL_2) MDIO45 WRITE (B,LN0_LS_SERDES_CONTROL_2) MDIO45 WRITE (B,LN3_LS_SERDES_CONTROL_3) MDIO45 WRITE (B,LN2_LS_SERDES_CONTROL_3) MDIO45 WRITE (B,LN1_LS_SERDES_CONTROL_3) MDIO45 WRITE (B,LN0_LS_SERDES_CONTROL_3) MDIO45 WRITE (B,HS_OVERLAY_CONTROL) MDIO45 WRITE (B,LS_OVERLAY_CONTROL) MDIO45 WRITE (B,LOOPBACK_TP_CONTROL) MDIO45 WRITE (B,LS_CONFIG_CONTROL) MDIO45 WRITE (B,LN3_LS_CH_CONTROL_1) MDIO45 WRITE (B,LN2_LS_CH_CONTROL_1) MDIO45 WRITE (B,LN1_LS_CH_CONTROL_1) MDIO45 WRITE (B,LN0_LS_CH_CONTROL_1) MDIO45 WRITE (B,HS_CH_CONTROL_1) //MDIO45 WRITE IMM (0x0,0x1E,0x8020,0x0200) MDIO45 WRITE (B,VS_SERDES_CFG_OVERRIDE_CTRL) MDIO45 WRITE FUNC (B,LS_PLL_MULT_OVERRIDE,0x0) MDIO45 WRITE FUNC (B,LS_RATE_OVERRIDE,0x0) MDIO45 WRITE FUNC (B,HS_PLL_MULT_OVERRIDE,0x0) MDIO45 WRITE FUNC (B,HS_RATE_OVERRIDE,0x0) MDIO45 WRITE FUNC (B,HS_FIRUPT_OVERRIDE,0x1) MDIO45 WRITE FUNC (B,HS_ENRX_OVERRIDE,0x0) MDIO45 WRITE FUNC (B,HS_AZCAL_OVERRIDE,0x0) MDIO45 WRITE FUNC (B,HS_ENTRACK_OVERRIDE,0x0) MDIO45 WRITE FUNC (B,HS_EQHLD_OVERRIDE,0x0) MDIO45 WRITE FUNC (B,HS_TWCRF_OVERRIDE,0x0) MDIO45 WRITE FUNC (B,HS_TWPOST2_OVERRIDE,0x0) MDIO45 WRITE FUNC (B,HS_TWPOST_OVERRIDE,0x0) MDIO45 WRITE FUNC (B,HS_TWPRE_OVERRIDE,0x0) MDIO45 WRITE FUNC (B,HS_SWING_OVERRIDE,0x0) //MDIO45 WRITE IMM (0x0,0x1E,0x8021,0x006F) MDIO45 WRITE (B,AUTO_CLKOUT_CONTROL) MDIO45 WRITE FUNC (B,HS_PLL_LOCK_CHECK_DISABLE,0x1) MDIO45 WRITE FUNC (B,HS_LOS_CHECK_DISABLE,0x1) MDIO45 WRITE FUNC (B,SYNC_STATUS_CHECK_DISABLE,0x0) MDIO45 WRITE (B,PMA_CONTROL_1) MDIO45 WRITE (B,KR_TRAIN_CONTROL) MDIO45 WRITE (B,KR_FEC_CONTROL) MDIO45 WRITE FUNC (B,KR_FEC_ERR_IND_EN,0x0) MDIO45 WRITE FUNC (B,KR_FEC_EN,0x0) MDIO45 WRITE (B,KR_VS_FIFO_CONTROL_1) MDIO45 WRITE (B,KR_VS_TP_GEN_CONTROL) MDIO45 WRITE (B,KR_VS_TP_VER_CONTROL) MDIO45 WRITE (B,KR_VS_CTC_ERR_CODE_LN0) MDIO45 WRITE (B,KR_VS_CTC_ERR_CODE_LN1) MDIO45 WRITE (B,KR_VS_CTC_ERR_CODE_LN2) MDIO45 WRITE (B,KR_VS_CTC_ERR_CODE_LN3) MDIO45 WRITE (B,PCS_CONTROL) MDIO45 WRITE (B,PCS_TP_SEED_A0) MDIO45 WRITE (B,PCS_TP_SEED_A1) MDIO45 WRITE (B,PCS_TP_SEED_A2) MDIO45 WRITE (B,PCS_TP_SEED_A3) MDIO45 WRITE (B,PCS_TP_SEED_B0) MDIO45 WRITE (B,PCS_TP_SEED_B1) MDIO45 WRITE (B,PCS_TP_SEED_B2) MDIO45 WRITE (B,PCS_TP_SEED_B3) MDIO45 WRITE (B,PCS_TP_CONTROL) MDIO45 WRITE (B,PCS_VS_CONTROL) MDIO45 WRITE (B,AN_CONTROL) MDIO45 WRITE (B,AN_ADVERTISEMENT_1) MDIO45 WRITE (B,AN_ADVERTISEMENT_2) MDIO45 WRITE (B,AN_ADVERTISEMENT_3) MDIO45 WRITE (B,AN_XNP_TRANSMIT_1) MDIO45 WRITE (B,AN_XNP_TRANSMIT_2) MDIO45 WRITE (B,AN_XNP_TRANSMIT_3) //******************************************************************************************** // CH C Provisioning //******************************************************************************************** MDIO45 WRITE (C,CHANNEL_CONTROL_1) MDIO45 WRITE (C,HS_SERDES_CONTROL_1) MDIO45 WRITE (C,HS_SERDES_CONTROL_2) MDIO45 WRITE (C,HS_SERDES_CONTROL_3) MDIO45 WRITE (C,HS_SERDES_CONTROL_4) MDIO45 WRITE (C,LS_SERDES_CONTROL_1) MDIO45 WRITE (C,LN3_LS_SERDES_CONTROL_2) MDIO45 WRITE (C,LN2_LS_SERDES_CONTROL_2) MDIO45 WRITE (C,LN1_LS_SERDES_CONTROL_2) MDIO45 WRITE (C,LN0_LS_SERDES_CONTROL_2) MDIO45 WRITE (C,LN3_LS_SERDES_CONTROL_3) MDIO45 WRITE (C,LN2_LS_SERDES_CONTROL_3) MDIO45 WRITE (C,LN1_LS_SERDES_CONTROL_3) MDIO45 WRITE (C,LN0_LS_SERDES_CONTROL_3) MDIO45 WRITE (C,HS_OVERLAY_CONTROL) MDIO45 WRITE (C,LS_OVERLAY_CONTROL) MDIO45 WRITE (C,LOOPBACK_TP_CONTROL) MDIO45 WRITE (C,LS_CONFIG_CONTROL) MDIO45 WRITE (C,LN3_LS_CH_CONTROL_1) MDIO45 WRITE (C,LN2_LS_CH_CONTROL_1) MDIO45 WRITE (C,LN1_LS_CH_CONTROL_1) MDIO45 WRITE (C,LN0_LS_CH_CONTROL_1) MDIO45 WRITE (C,HS_CH_CONTROL_1) //MDIO45 WRITE IMM (0x0,0x1E,0x8020,0x0200) MDIO45 WRITE (C,VS_SERDES_CFG_OVERRIDE_CTRL) MDIO45 WRITE FUNC (C,LS_PLL_MULT_OVERRIDE,0x0) MDIO45 WRITE FUNC (C,LS_RATE_OVERRIDE,0x0) MDIO45 WRITE FUNC (C,HS_PLL_MULT_OVERRIDE,0x0) MDIO45 WRITE FUNC (C,HS_RATE_OVERRIDE,0x0) MDIO45 WRITE FUNC (C,HS_FIRUPT_OVERRIDE,0x1) MDIO45 WRITE FUNC (C,HS_ENRX_OVERRIDE,0x0) MDIO45 WRITE FUNC (C,HS_AZCAL_OVERRIDE,0x0) MDIO45 WRITE FUNC (C,HS_ENTRACK_OVERRIDE,0x0) MDIO45 WRITE FUNC (C,HS_EQHLD_OVERRIDE,0x0) MDIO45 WRITE FUNC (C,HS_TWCRF_OVERRIDE,0x0) MDIO45 WRITE FUNC (C,HS_TWPOST2_OVERRIDE,0x0) MDIO45 WRITE FUNC (C,HS_TWPOST_OVERRIDE,0x0) MDIO45 WRITE FUNC (C,HS_TWPRE_OVERRIDE,0x0) MDIO45 WRITE FUNC (C,HS_SWING_OVERRIDE,0x0) //MDIO45 WRITE IMM (0x0,0x1E,0x8021,0x006F) MDIO45 WRITE (C,AUTO_CLKOUT_CONTROL) MDIO45 WRITE FUNC (C,HS_PLL_LOCK_CHECK_DISABLE,0x1) MDIO45 WRITE FUNC (C,HS_LOS_CHECK_DISABLE,0x1) MDIO45 WRITE FUNC (C,SYNC_STATUS_CHECK_DISABLE,0x0) MDIO45 WRITE (C,PMA_CONTROL_1) MDIO45 WRITE (C,KR_TRAIN_CONTROL) MDIO45 WRITE (C,KR_FEC_CONTROL) MDIO45 WRITE FUNC (C,KR_FEC_ERR_IND_EN,0x0) MDIO45 WRITE FUNC (C,KR_FEC_EN,0x0) MDIO45 WRITE (C,KR_VS_FIFO_CONTROL_1) MDIO45 WRITE (C,KR_VS_TP_GEN_CONTROL) MDIO45 WRITE (C,KR_VS_TP_VER_CONTROL) MDIO45 WRITE (C,KR_VS_CTC_ERR_CODE_LN0) MDIO45 WRITE (C,KR_VS_CTC_ERR_CODE_LN1) MDIO45 WRITE (C,KR_VS_CTC_ERR_CODE_LN2) MDIO45 WRITE (C,KR_VS_CTC_ERR_CODE_LN3) MDIO45 WRITE (C,PCS_CONTROL) MDIO45 WRITE (C,PCS_TP_SEED_A0) MDIO45 WRITE (C,PCS_TP_SEED_A1) MDIO45 WRITE (C,PCS_TP_SEED_A2) MDIO45 WRITE (C,PCS_TP_SEED_A3) MDIO45 WRITE (C,PCS_TP_SEED_B0) MDIO45 WRITE (C,PCS_TP_SEED_B1) MDIO45 WRITE (C,PCS_TP_SEED_B2) MDIO45 WRITE (C,PCS_TP_SEED_B3) MDIO45 WRITE (C,PCS_TP_CONTROL) MDIO45 WRITE (C,PCS_VS_CONTROL) MDIO45 WRITE (C,AN_CONTROL) MDIO45 WRITE (C,AN_ADVERTISEMENT_1) MDIO45 WRITE (C,AN_ADVERTISEMENT_2) MDIO45 WRITE (C,AN_ADVERTISEMENT_3) MDIO45 WRITE (C,AN_XNP_TRANSMIT_1) MDIO45 WRITE (C,AN_XNP_TRANSMIT_2) MDIO45 WRITE (C,AN_XNP_TRANSMIT_3) //******************************************************************************************** // CH D Provisioning //******************************************************************************************** MDIO45 WRITE (D,CHANNEL_CONTROL_1) MDIO45 WRITE (D,HS_SERDES_CONTROL_1) MDIO45 WRITE (D,HS_SERDES_CONTROL_2) MDIO45 WRITE (D,HS_SERDES_CONTROL_3) MDIO45 WRITE (D,HS_SERDES_CONTROL_4) MDIO45 WRITE (D,LS_SERDES_CONTROL_1) MDIO45 WRITE (D,LN3_LS_SERDES_CONTROL_2) MDIO45 WRITE (D,LN2_LS_SERDES_CONTROL_2) MDIO45 WRITE (D,LN1_LS_SERDES_CONTROL_2) MDIO45 WRITE (D,LN0_LS_SERDES_CONTROL_2) MDIO45 WRITE (D,LN3_LS_SERDES_CONTROL_3) MDIO45 WRITE (D,LN2_LS_SERDES_CONTROL_3) MDIO45 WRITE (D,LN1_LS_SERDES_CONTROL_3) MDIO45 WRITE (D,LN0_LS_SERDES_CONTROL_3) MDIO45 WRITE (D,HS_OVERLAY_CONTROL) MDIO45 WRITE (D,LS_OVERLAY_CONTROL) MDIO45 WRITE (D,LOOPBACK_TP_CONTROL) MDIO45 WRITE (D,LS_CONFIG_CONTROL) MDIO45 WRITE (D,LN3_LS_CH_CONTROL_1) MDIO45 WRITE (D,LN2_LS_CH_CONTROL_1) MDIO45 WRITE (D,LN1_LS_CH_CONTROL_1) MDIO45 WRITE (D,LN0_LS_CH_CONTROL_1) MDIO45 WRITE (D,HS_CH_CONTROL_1) //MDIO45 WRITE IMM (0x0,0x1E,0x8020,0x0200) MDIO45 WRITE (D,VS_SERDES_CFG_OVERRIDE_CTRL) MDIO45 WRITE FUNC (D,LS_PLL_MULT_OVERRIDE,0x0) MDIO45 WRITE FUNC (D,LS_RATE_OVERRIDE,0x0) MDIO45 WRITE FUNC (D,HS_PLL_MULT_OVERRIDE,0x0) MDIO45 WRITE FUNC (D,HS_RATE_OVERRIDE,0x0) MDIO45 WRITE FUNC (D,HS_FIRUPT_OVERRIDE,0x1) MDIO45 WRITE FUNC (D,HS_ENRX_OVERRIDE,0x0) MDIO45 WRITE FUNC (D,HS_AZCAL_OVERRIDE,0x0) MDIO45 WRITE FUNC (D,HS_ENTRACK_OVERRIDE,0x0) MDIO45 WRITE FUNC (D,HS_EQHLD_OVERRIDE,0x0) MDIO45 WRITE FUNC (D,HS_TWCRF_OVERRIDE,0x0) MDIO45 WRITE FUNC (D,HS_TWPOST2_OVERRIDE,0x0) MDIO45 WRITE FUNC (D,HS_TWPOST_OVERRIDE,0x0) MDIO45 WRITE FUNC (D,HS_TWPRE_OVERRIDE,0x0) MDIO45 WRITE FUNC (D,HS_SWING_OVERRIDE,0x0) //MDIO45 WRITE IMM (0x0,0x1E,0x8021,0x006F) MDIO45 WRITE (D,AUTO_CLKOUT_CONTROL) MDIO45 WRITE FUNC (D,HS_PLL_LOCK_CHECK_DISABLE,0x1) MDIO45 WRITE FUNC (D,HS_LOS_CHECK_DISABLE,0x1) MDIO45 WRITE FUNC (D,SYNC_STATUS_CHECK_DISABLE,0x0) MDIO45 WRITE (D,PMA_CONTROL_1) MDIO45 WRITE (D,KR_TRAIN_CONTROL) MDIO45 WRITE (D,KR_FEC_CONTROL) MDIO45 WRITE FUNC (D,KR_FEC_ERR_IND_EN,0x0) MDIO45 WRITE FUNC (D,KR_FEC_EN,0x0) MDIO45 WRITE (D,KR_VS_FIFO_CONTROL_1) MDIO45 WRITE (D,KR_VS_TP_GEN_CONTROL) MDIO45 WRITE (D,KR_VS_TP_VER_CONTROL) MDIO45 WRITE (D,KR_VS_CTC_ERR_CODE_LN0) MDIO45 WRITE (D,KR_VS_CTC_ERR_CODE_LN1) MDIO45 WRITE (D,KR_VS_CTC_ERR_CODE_LN2) MDIO45 WRITE (D,KR_VS_CTC_ERR_CODE_LN3) MDIO45 WRITE (D,PCS_CONTROL) MDIO45 WRITE (D,PCS_TP_SEED_A0) MDIO45 WRITE (D,PCS_TP_SEED_A1) MDIO45 WRITE (D,PCS_TP_SEED_A2) MDIO45 WRITE (D,PCS_TP_SEED_A3) MDIO45 WRITE (D,PCS_TP_SEED_B0) MDIO45 WRITE (D,PCS_TP_SEED_B1) MDIO45 WRITE (D,PCS_TP_SEED_B2) MDIO45 WRITE (D,PCS_TP_SEED_B3) MDIO45 WRITE (D,PCS_TP_CONTROL) MDIO45 WRITE (D,PCS_VS_CONTROL) MDIO45 WRITE (D,AN_CONTROL) MDIO45 WRITE (D,AN_ADVERTISEMENT_1) MDIO45 WRITE (D,AN_ADVERTISEMENT_2) MDIO45 WRITE (D,AN_ADVERTISEMENT_3) MDIO45 WRITE (D,AN_XNP_TRANSMIT_1) MDIO45 WRITE (D,AN_XNP_TRANSMIT_2) MDIO45 WRITE (D,AN_XNP_TRANSMIT_3) //******************************************************************************************** // Output Clock Provisioning //******************************************************************************************** MDIO45 WRITE (GLOBAL,LS_CLKOUT_CONTROL) MDIO45 WRITE (GLOBAL,HS_TX_CLKOUT_CONTROL) MDIO45 WRITE (GLOBAL,LS_CLKOUT_PWRDWN_CONTROL) //******************************************************************************************** // Restart Auto Negotiation //******************************************************************************************** // Issue Auto Negotiate Reset MDIO45 WRITE FUNC (A,AN_RESTART,0x1) MDIO45 READ (A,AN_CONTROL) MDIO45 WRITE FUNC (B,AN_RESTART,0x1) MDIO45 READ (B,AN_CONTROL) MDIO45 WRITE FUNC (C,AN_RESTART,0x1) MDIO45 READ (C,AN_CONTROL) MDIO45 WRITE FUNC (D,AN_RESTART,0x1) MDIO45 READ (D,AN_CONTROL) // The AN_RESTART bit is self clearing, but the GUI is not. Reset the bit in the GUI. // Not required in the customer's system application MDIO45 WRITE FUNC (A,AN_RESTART,0x0) MDIO45 WRITE FUNC (B,AN_RESTART,0x0) MDIO45 WRITE FUNC (C,AN_RESTART,0x0) MDIO45 WRITE FUNC (D,AN_RESTART,0x0) // Wait 2000mS WAIT(2000) //******************************************************************************************** // Verify HS_AZ_DONE, HS_AGC_LOCKED and LS/HS PLL Lock Status //******************************************************************************************** // Poll LS/HS_PLL_LOCK,HS_AZ_DONE,HS_AGC_LOCKED Bits MDIO45 READ UNTIL (A,CHANNEL_STATUS_1,0x1803,0x1803,1000) MDIO45 READ UNTIL (B,CHANNEL_STATUS_1,0x1803,0x1803,1000) MDIO45 READ UNTIL (C,CHANNEL_STATUS_1,0x1803,0x1803,1000) MDIO45 READ UNTIL (D,CHANNEL_STATUS_1,0x1803,0x1803,1000) //******************************************************************************************** // Verify Auto Negotiation Complete //******************************************************************************************** // Poll AN_COMPLETE,LINK_STATUS Bits MDIO45 READ UNTIL (A,AN_STATUS,0x0024,0x0024,1000) MDIO45 READ UNTIL (B,AN_STATUS,0x0024,0x0024,1000) MDIO45 READ UNTIL (C,AN_STATUS,0x0024,0x0024,1000) MDIO45 READ UNTIL (D,AN_STATUS,0x0024,0x0024,1000) //******************************************************************************************** // Verify Link Training Complete //******************************************************************************************** // Poll KR_TRAINING_FAIL,KR_RX_STATUS Bits MDIO45 READ UNTIL (A,KR_TRAIN_STATUS,0x0009,0x0001,1000) MDIO45 READ UNTIL (B,KR_TRAIN_STATUS,0x0009,0x0001,1000) MDIO45 READ UNTIL (C,KR_TRAIN_STATUS,0x0009,0x0001,1000) MDIO45 READ UNTIL (D,KR_TRAIN_STATUS,0x0009,0x0001,1000) //******************************************************************************************** // Verify 10GKR Mode //******************************************************************************************** // Poll AN_10G_KR Bit MDIO45 READ UNTIL (A,AN_BP_STATUS,0x0008,0x0008,1000) MDIO45 READ UNTIL (B,AN_BP_STATUS,0x0008,0x0008,1000) MDIO45 READ UNTIL (C,AN_BP_STATUS,0x0008,0x0008,1000) MDIO45 READ UNTIL (D,AN_BP_STATUS,0x0008,0x0008,1000) //******************************************************************************************** // Clear Latched Registers //******************************************************************************************** // Read and Clear Latched Status Register Bits MDIO45 READ (A,CHANNEL_STATUS_1) MDIO45 READ (B,CHANNEL_STATUS_1) MDIO45 READ (C,CHANNEL_STATUS_1) MDIO45 READ (D,CHANNEL_STATUS_1) // Read and Clear Error Counters MDIO45 READ (A,HS_ERROR_COUNTER) MDIO45 READ (B,HS_ERROR_COUNTER) MDIO45 READ (C,HS_ERROR_COUNTER) MDIO45 READ (D,HS_ERROR_COUNTER) MDIO45 READ (A,LS_LN0_ERROR_COUNTER) MDIO45 READ (B,LS_LN0_ERROR_COUNTER) MDIO45 READ (C,LS_LN0_ERROR_COUNTER) MDIO45 READ (D,LS_LN0_ERROR_COUNTER) MDIO45 READ (A,LS_LN1_ERROR_COUNTER) MDIO45 READ (B,LS_LN1_ERROR_COUNTER) MDIO45 READ (C,LS_LN1_ERROR_COUNTER) MDIO45 READ (D,LS_LN1_ERROR_COUNTER) MDIO45 READ (A,LS_LN2_ERROR_COUNTER) MDIO45 READ (B,LS_LN2_ERROR_COUNTER) MDIO45 READ (C,LS_LN2_ERROR_COUNTER) MDIO45 READ (D,LS_LN2_ERROR_COUNTER) MDIO45 READ (A,LS_LN3_ERROR_COUNTER) MDIO45 READ (B,LS_LN3_ERROR_COUNTER) MDIO45 READ (C,LS_LN3_ERROR_COUNTER) MDIO45 READ (D,LS_LN3_ERROR_COUNTER) // Read and Clear Latched LS Status Register Bits MDIO45 READ (A,LN0_LS_STATUS_1) MDIO45 READ (A,LN1_LS_STATUS_1) MDIO45 READ (A,LN2_LS_STATUS_1) MDIO45 READ (A,LN3_LS_STATUS_1) MDIO45 READ (B,LN0_LS_STATUS_1) MDIO45 READ (B,LN1_LS_STATUS_1) MDIO45 READ (B,LN2_LS_STATUS_1) MDIO45 READ (B,LN3_LS_STATUS_1) MDIO45 READ (C,LN0_LS_STATUS_1) MDIO45 READ (C,LN1_LS_STATUS_1) MDIO45 READ (C,LN2_LS_STATUS_1) MDIO45 READ (C,LN3_LS_STATUS_1) MDIO45 READ (D,LN0_LS_STATUS_1) MDIO45 READ (D,LN1_LS_STATUS_1) MDIO45 READ (D,LN2_LS_STATUS_1) MDIO45 READ (D,LN3_LS_STATUS_1) // Read and Clear Latched Status Register Bits MDIO45 READ (A,PMA_STATUS_1) MDIO45 READ (B,PMA_STATUS_1) MDIO45 READ (C,PMA_STATUS_1) MDIO45 READ (D,PMA_STATUS_1) MDIO45 READ (A,PMA_STATUS_2) MDIO45 READ (B,PMA_STATUS_2) MDIO45 READ (C,PMA_STATUS_2) MDIO45 READ (D,PMA_STATUS_2) MDIO45 READ (A,PCS_STATUS_1) MDIO45 READ (B,PCS_STATUS_1) MDIO45 READ (C,PCS_STATUS_1) MDIO45 READ (D,PCS_STATUS_1) MDIO45 READ (A,PCS_STATUS_2) MDIO45 READ (B,PCS_STATUS_2) MDIO45 READ (C,PCS_STATUS_2) MDIO45 READ (D,PCS_STATUS_2) //******************************************************************************************** // Operational Mode Status //******************************************************************************************** // Read and Verify the Operational Mode Status MDIO45 READ UNTIL (A,CHANNEL_STATUS_1,0xFFFF,0x5C03,0) MDIO45 READ UNTIL (B,CHANNEL_STATUS_1,0xFFFF,0x5C03,0) MDIO45 READ UNTIL (C,CHANNEL_STATUS_1,0xFFFF,0x5C03,0) MDIO45 READ UNTIL (D,CHANNEL_STATUS_1,0xFFFF,0x5C03,0) MDIO45 READ UNTIL (A,HS_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (B,HS_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (C,HS_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (D,HS_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (A,LS_LN0_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (B,LS_LN0_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (C,LS_LN0_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (D,LS_LN0_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (A,LS_LN1_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (B,LS_LN1_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (C,LS_LN1_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (D,LS_LN1_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (A,LS_LN2_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (B,LS_LN2_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (C,LS_LN2_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (D,LS_LN2_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (A,LS_LN3_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (B,LS_LN3_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (C,LS_LN3_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (D,LS_LN3_ERROR_COUNTER,0xFFFF,0x0000,0) MDIO45 READ UNTIL (A,LN0_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (A,LN1_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (A,LN2_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (A,LN3_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (B,LN0_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (B,LN1_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (B,LN2_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (B,LN3_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (C,LN0_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (C,LN1_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (C,LN2_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (C,LN3_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (D,LN0_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (D,LN1_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (D,LN2_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (D,LN3_LS_STATUS_1,0x0508,0x0100,0) MDIO45 READ UNTIL (A,PMA_STATUS_1,0x0084,0x0004,0) MDIO45 READ UNTIL (B,PMA_STATUS_1,0x0084,0x0004,0) MDIO45 READ UNTIL (C,PMA_STATUS_1,0x0084,0x0004,0) MDIO45 READ UNTIL (D,PMA_STATUS_1,0x0084,0x0004,0) MDIO45 READ UNTIL (A,PCS_STATUS_1,0x0084,0x0004,0) MDIO45 READ UNTIL (B,PCS_STATUS_1,0x0084,0x0004,0) MDIO45 READ UNTIL (C,PCS_STATUS_1,0x0084,0x0004,0) MDIO45 READ UNTIL (D,PCS_STATUS_1,0x0084,0x0004,0)

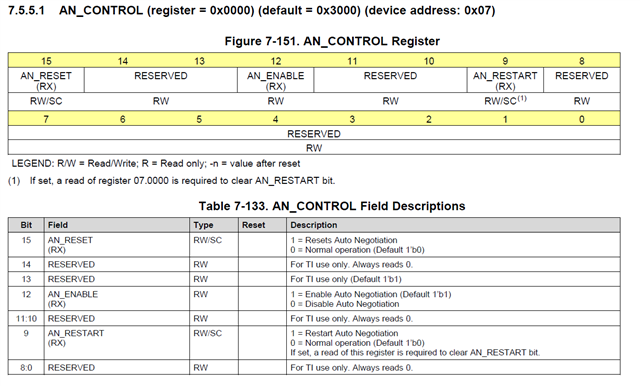

See register description below taken from datasheet for disabling AN.

Thanks,

Rodrigo Natal