Hello Team,

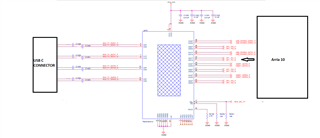

I am using TMUXHS4412 in my design. I have connected the mux to the Arra10 FPGA Serdes (Bank 1G,1H,1I) (Arria 10 Part no:10AX057N2F40E2SG).The supply voltage provided for the MUX is 3.3V.The Bank voltage provided for the Serdes bank is 1.03V

My application is both USB (Host and Device) and DP (Source and sink) data transfer at a speed upto10Gbps.

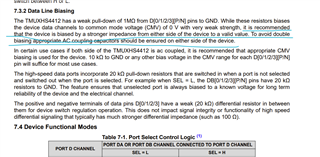

could you please let me know, Will there be any voltage compatibility issues with the MUX and Arria 10 Serdes. And also will there be a problem with the common-mode voltage of both mux and Arria 10 Serdes.

And also do I need to place capacitors on both sides of the MUX or only the Type C connector side is fine.

I am attaching the block diagram for capacitor placement in my circuit.

Regards,

Tensil Sebastian