Other Parts Discussed in Thread: DS250DF410

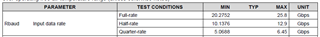

Hello, I'm trying to understand the relation between the clock frequency (that's provided externally through RX0N and RX0P) and the PRBS data rate.

For example, what should be the supplied clock frequency in order to achieve a PRBS11 with 20 Gpbs data rate.

Thank you.