Other Parts Discussed in Thread: SN65DSI83

Hello David,

Sorry for late reply. this is same topic as previous one.

SN65DSI83-Q1: Timing variation of LVDS output - Interface forum - Interface - TI E2E support forums

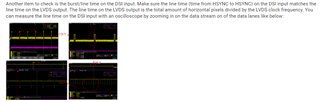

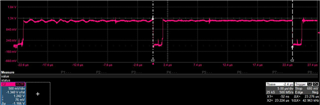

Here is measurement result as you requested.it shows 23.276us.

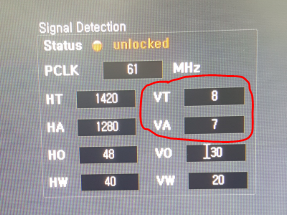

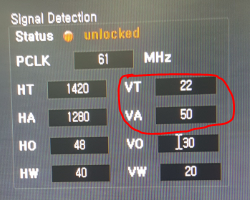

They OLDI output is 61MHz, so 1/61MHz*1420(Htotal)=23.278us. so I understand DSI input doesn't show problem.

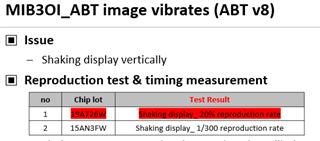

and only 2 pixel of front porch is shifted to back porch when issue happen as below table.(normal : 50/50 for front/back porch, flicker issue case: 48/52 for front/back porch value could be found)

|

Parameters |

Setting(normal case) |

Real Measured value in issue case. |

|

|

v_period |

720 |

720 |

720 |

|

v_pulse |

20 |

20 |

20 |

|

v_back_porch |

30 |

30 |

30 |

|

v_front_porch |

30 |

30 |

30 |

|

v_active_width |

640 |

640 |

640 |

|

h_period |

1420 |

1420 |

1420 |

|

h_pulse |

40 |

40 |

40 |

|

h_back_porch |

50 |

52 |

50 |

|

h_front_porch |

50 |

48 |

50 |

|

h_active_width |

1280 |

1280 |

1280 |

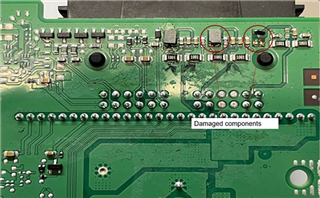

so customer wants to know if device has some limitation when generate sync timing.

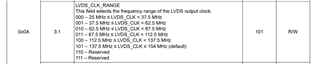

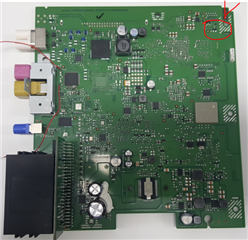

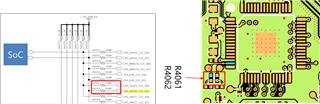

Can you help further verification?? there is no sync delay issue in current CSR register??(pls refer to attached)

Test result for SN65DSI83.pptx

Thank you.