Other Parts Discussed in Thread: SN75LVDS83

Hi team,

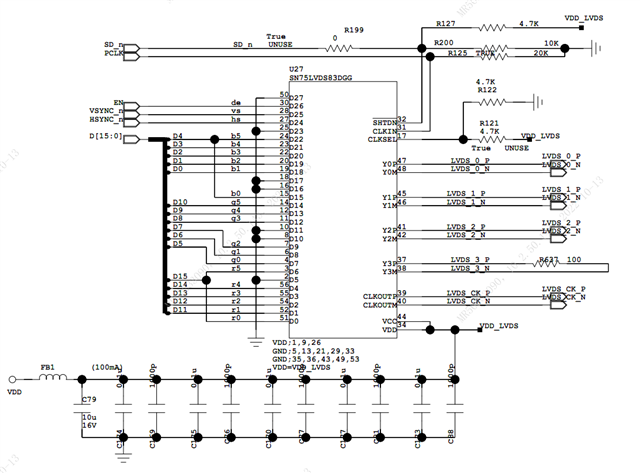

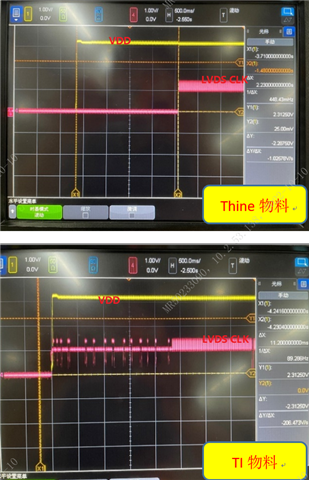

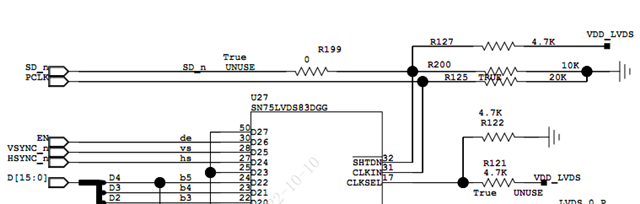

Customer test SN75LVDS83B and its LVDS CLKOUT, and customer found that when VDD is applied without RGB input, what will be the status of CLKOUT? Customer test result as below, could you pls help to explain why the CLKOUT swing around common voltage? Top is competitor test result, bottom is TI result.

Thx~

Rayna