Hi team,

Customer has meet an issue on SN75LVDS83B.

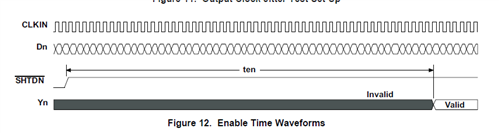

After power up VDD and SHTDN is tied on VDD, CLKIN pin accept a period of CLK from CPU but no valid data. Then customer found some abnormal pulsers output at Y0M. you can refer to attached waveform. The left graph shows LVDS input signal on D0-D7 (green) and output signal on Y0M (yellow). The right graph shows CLKIN(green) and output signal on Y0M (yellow). The abnormal output appears before and after the period of clk without input.

I’m suspecting that when CLKIN has input, the device with send clk signal to 7 channels and at that time, no data to output, which may cause some crosstalk from CLK to output. I’m not sure about that.

Could you pls help to comment on this issue? Thanks!

Thanks!

BR.

Rayna