Part Number: DS90UB948-Q1

hi team,

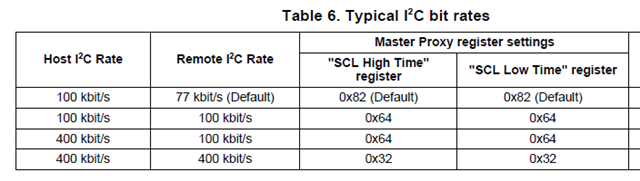

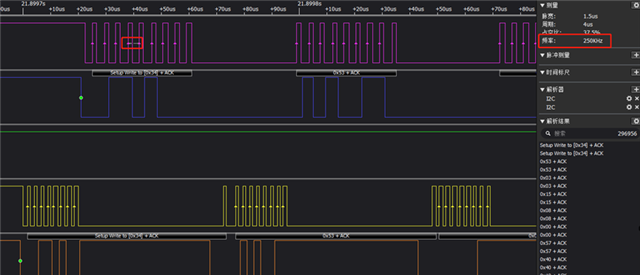

Can you share some materials on the I2C SCL setting of deserializer? Customer found the SCL setting is not aligned with register setting, 948: 0x26=0x17; 0x27=0x17 (should be 400kHz but the test results is 250kHz)

948 I2C waveforms: SCL=250kHz

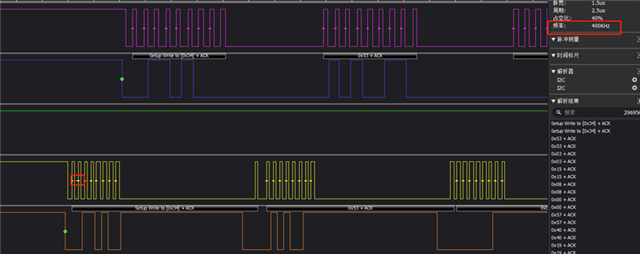

949 I2C waveforms

Regards,

Dongbao