Other Parts Discussed in Thread: DSI-TUNER, SN65DSI86, , SN65DSI85, SN65DSI84, SN65DSI83, SN65DSI83Q1-EVM

Hello everyone,

i already got the display to work with the SN65DSI86, in particular the on the SN65DSI86-EVM thanks to Zach Dryer who pointed out, that i need the excel-sheet for that and that the DSI-Tuner will not work with the Chip.

I got the eDP part working and have to wait for our programmers to get ready to do the MIPI part.

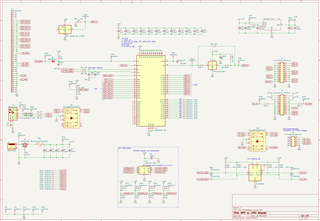

In the meantime i need to test the SN65DSI84-Q1 chip with the display aswell. I made a small pcb with the chip and the chip works and i can access it via i2c. The vcore of 1V is also good.

But i have the same problem with generating the necessery i2c settings as i had with the other chip.

My display has the following edid data, that i read out of a eDP to LVDS chip that works with that display on another pcb:

The settings of the excel sheet that i used to get the testpattern to work with the SN65DSI86 are the following:

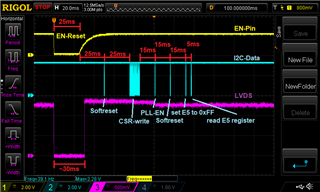

The DSI-Tuner does not accept horizontal and vertical blanking pixels. It only accepts horizontal and vertical backporch so i calculated the values according to the datasheet of the ic on page 40:

BackPorch = Blanking - (Offset or FrontPorch + PulseWidth)

I got the following values:

The DSI-Tuner settings are now the following:

My first priority is to get the testpattern to work, so if the MIPI settings are a bit wrong i am okay for the moment.

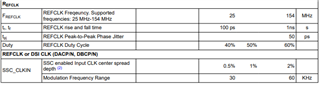

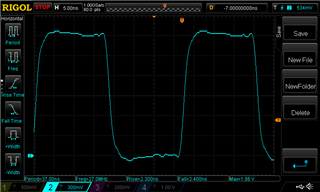

My custom pcb has a 27Mhz oscillator directly connected to the REFCLK input. Because the datasheet of the display specifies a 51.21 Mhz Clock for the display i deemed it okay to use that and use the times two multiplier in the ic. The clock can be between 44,9 and 63 Mhz according to the datasheed of the display.

Here are the timing parameters directly from the datasheet of the display:

i am thankfull for any ideas. I will post the schematic of the pcb if necessary

Thank you very much,

Marc