Hello TI-Members,

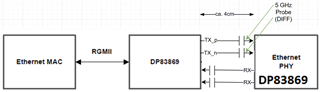

I have the following setup (1x DP83869HM in bridge-mode, 1x DP83869HM in SGMII-to-Copper mode):

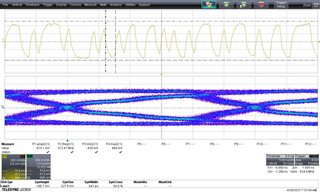

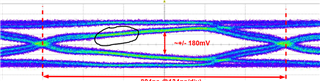

I measured signal integrity (with a 5 GHz differential probe and 6 GHz scope) at the input of SGMII-to-Copper PHY (after AC-caps):

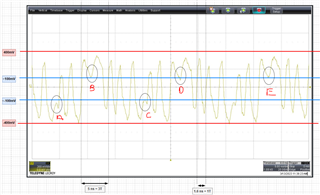

These are my results:

My questions are:

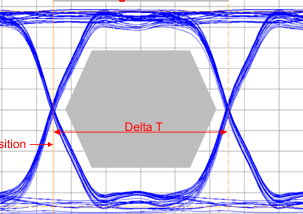

- How to know, if e.g. sample position "B" is a period of 1-1-1 or if this is a period of 1-0-1 but the zero voltage level is not reached.

- What is the SGMII input voltage treshold specification? I can't find this spec in the datasheet

- In the DS the SGMII output is specified with Output Differential Voltage = 1060 (min) / 1100 (typ) / 1140 (max)

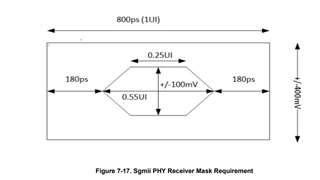

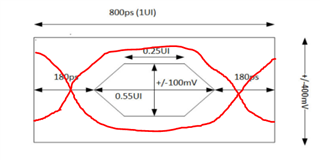

--- At the receiver the SGMII-signal is only between -400mV to 400 mV (800mV)

------ Does it mean that I have significant losses on the transmission lines?

Thx in advance!

Julian