Other Parts Discussed in Thread: DS90C387, TFP401

Hello,

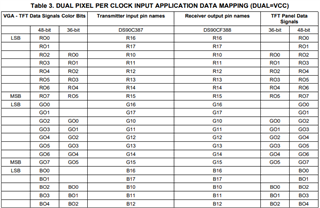

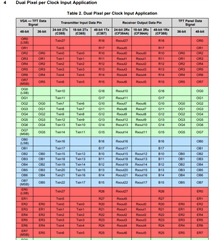

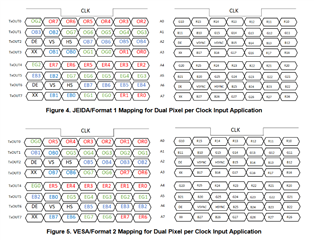

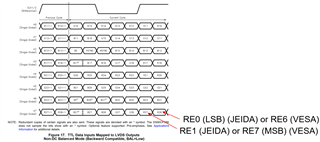

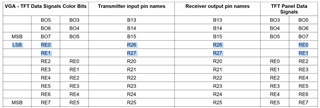

Im developing a HDMI to LVDS bridge using TFP401APZP with DS90C387VJDX/NOPB - This is a dual channel converter - I have already asked for help under part number DS90C387 and was told that i wont get any help as the issue is caused by TFP401A.

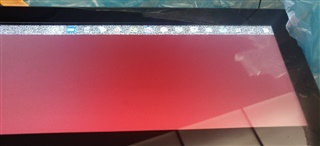

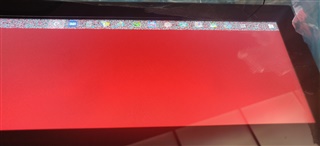

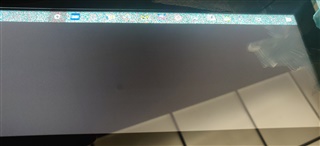

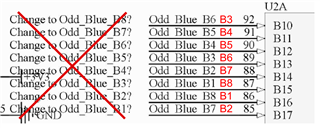

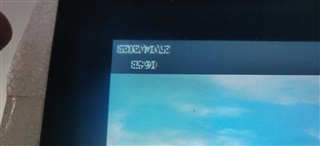

I am experiencing an issue with the display showing a distorted image.

I have attached the previous thread where i have outlined everything i have tried and the current configuration of the system. I have also attached images outlining the issues.

We have tried changing the configuration pins on both TFP401APZP and DS90C387VJDX/NOPB with no change in display or the display stopping completely.

We have chekced the differential pair impedance matching and length matching and chekced the length matching in the RGB outputs.

We have also tried to change the EDID but this either makes no difference or makes the display stop working.

Could you please help us with finding out what could be causing the issue, We would greatly ppreciate it.

Best Regards,

Kacper

00 FF FF FF FF FF FF 00 1D 85 01 24 01 00 00 00 20 12 01 04 A1 2B 1B 6D EF C5 C6 A3 57 4A 9C 23 12 4F 54 00 00 00 01 00 01 00 01 00 01 00 01 00 01 00 01 01 01 01 30 2A 80 18 71 68 8E 11 12 20 0A 08 40 6C 20 00 00 3E 00 00 00 FF 00 35 31 36 38 0A 20 20 20 20 20 20 20 20 00 00 00 FA 00 09 4F 01 00 01 00 01 00 01 00 01 00 0A 00 00 00 FC 00 4C 43 44 20 4D 4F 4E 49 54 4F 52 20 20 01 29 02 01 04 00 02 3A 80 18 71 38 2D 40 58 2C 45 00 D7 40 32 00 00 1E 01 1D 00 72 51 D0 1E 20 6E 28 55 00 D7 40 32 00 00 1E 01 1D 80 18 71 1C 16 20 58 2C 25 00 D7 40 32 00 00 9E 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 95