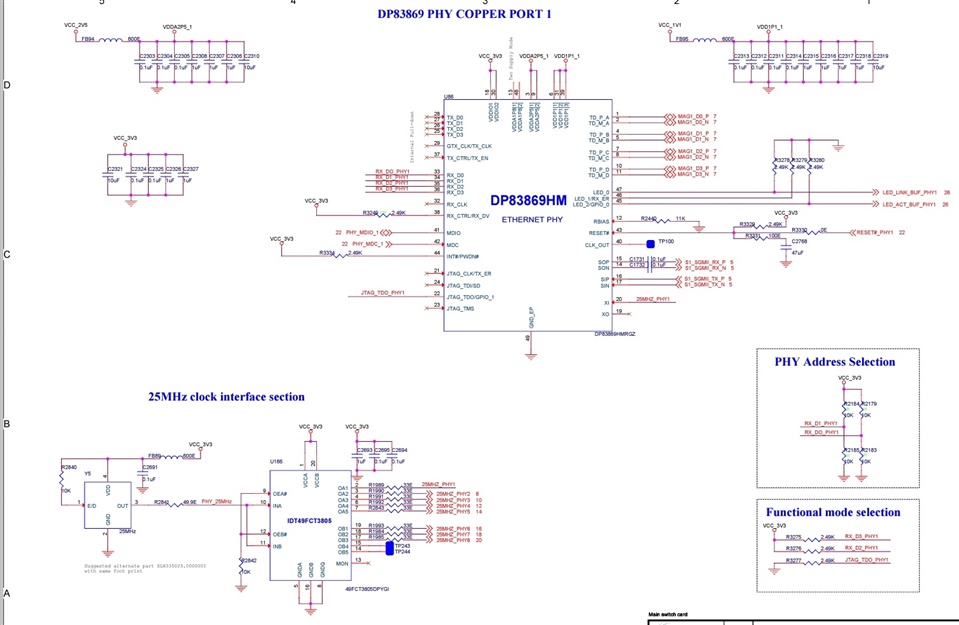

Part Number: DP83869HM

Other Parts Discussed in Thread: TM4C129DNCPDT, DP83869, USB-2-MDIO, MSP-EXP430G2ET

Hi,

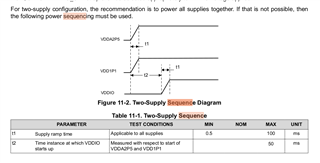

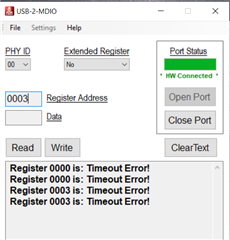

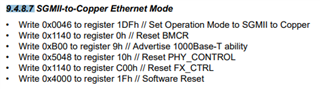

We are using DP83869HM PHY in our board for SGMII to Copper Ethernet Mode. The Strapping configuration has been followed as per the 9.5.1.2 Strap for DP83869HM Functional Mode Selection table in datasheet. The clock and Voltage levels also going proper to the PHY(CLOCK_OUT=25MHz), But still we are not able to detect link. We tried to access the PHY registers using the TM4C129DNCPDT controller but the PHY is not responding i.e., FFFF we are recieving as response. Please help us to access the PHY.