Other Parts Discussed in Thread: TMUXHS221

Dear Team,

May I ask how much Jitter and Latency will be added if it is used as a PCIe Gen5 CLK to channel switch?

Many Thanks,

Jimmy

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Jimmy,

Thank you for your question. As of now, we do not have this data. We will work to gather for you, but it will take some time.

What is the size of the opportunity and timeline of the project?

Best,

Stanton

Jimmy,

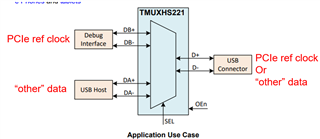

Are you/your customer aware of TMUXHS221? TMUXHS221 is our newest USB 2.0 2:1 mux, and TMUXHS221 has better performance (except in ESD). TMUXHS221 would be my top recommendation if this device works for your design requirements.

Best,

Stanton

Hi Slw,

Thanks for your suggestion. Do we have 1:2 mux solution?

Many Thanks,

Jimmy

Hi SLW,

Thanks for your great support.

When TMUXHS221 is used for PCIe 5.0 clock channel switching, it only has the function of MUX but not the function of DEMUX, right?

Please help me to recommend 4:1 MUX, 4:2 MUX or 8:2MUX for PCIe 5.0 clock, thanks~

Jimmy

Hi Jimmy,

TMUXHS221 can function as demux when used for PCIe gen 5.0 clock channel switching.

We only have 2:1 mux solutions suitable for PCIe. We do not have other pin configurations (4:1 MUX, 4:2 MUX or 8:2MUX). You may be able to cascade 2:1 muxes, but this will increase loss. To compensate for the loss, you may need to use PCIe signal conditioning.

Best,

Stanton

We only have 2:1 mux solutions suitable for PCIe. We do not have other pin configurations (4:1 MUX, 4:2 MUX or 8:2MUX). You may be able to cascade 2:1 muxes, but this will increase loss. To compensate for the loss, you may need to use PCIe signal conditioning.

Hi SLW,

Thanks for your great support.

There are still a few questions to ask about TMUXHS221:

1. Does TMUXHS221 support three PCIe Gen5 clk clock architectures: CC, SRIS, and SRNS?

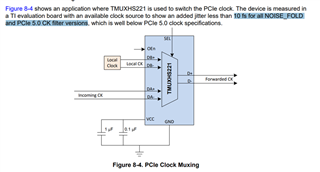

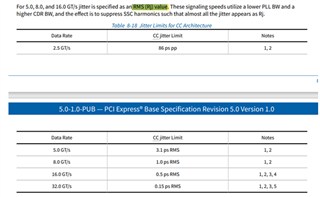

2. I don't understand the meaning of 10 fs for all NOISE_FOLD and PCIe 5.0 CLK filter versions. Does 10 fs refer to the increased RMS Jitter? PCI_Express_Base_5.0 protocol stipulates RMS (Rj) value

3. When TMUXHS221 is used as DEMUX for PCIe 5.0 CLK, have you done relevant tests? When used for PCIe 5.0 CLK in the specification, only the Diagram when used as MUX is drawn

4. When TMUXHS221 is used for PCIe 5.0 CLK, is the Propagation delay measured?

Many Thanks,

Jimmy

Hi Jimmy,

FYI I followed up in an email.

Best,

Stanton