Hi,

We have a setup where we aggregate 8x625 Mbps links to 1x5.00 Gbps link. We only use the TLK10081 in TX mode.

With the data generator chip in idle mode it generates 0xBC characters. We configured the TLK10081 to replace this charackter with 0x5C on lane 0. This all looks fine and we receive the 0xBC and 0x5C characters on our fpga.

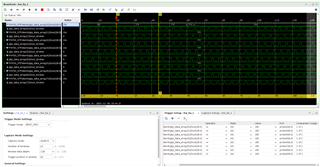

But when we trigger on our FPGA on not the 0xBC char (note that we have replaced the 0x5C with 0xBC again inside the FPGA) we get occasionally a pattern of

"6x 0xFE - 4x"idle char" (0xFD in our case) - 1x 0xFE". Those chars are all marked as control characters.

The sequence we get: /K30.7/K30.7/K30.7/K30.7/K30.7/K30.7/K29.7/K29.7/K29.7/K29.7/K30.7/

our TLK configuration is:

{ TLK81_GLOBAL_CONTROL, 0x8610 }, // Reset{ TLK81_CHANNEL_CONTROL, 0x0000 }, // Disable link training{ TLK81_HS_SERDES_CONTROL_1, 0x8315 }, // Set PLL multiplier to 8x{ TLK81_HS_SERDES_CONTROL_2, 0xA940 }, /* Set HS TX rate to half rate Disable HS RX */{ TLK81_HS_SERDES_CONTROL_3, 0x1540 }, // Disables high frequency peaking.{ TLK81_HS_TP_CONTROL, 0x0520 }, /* Disable HS Test Pattern (0x2520)(0x2200)(0x2020)(0x0520) Set HS tp 2^7 Set LS PRBS 2^7 Disable Deep Remote Loopback */{ TLK81_LS_SERDES_CONTROL_1, 0x8110 }, // Set LS_MPY to 4 times{ TLK81_LS_CH_CONTROL, 0x0001},{ TLK81_LS_SERDES_CONTROL_2, 0xDE02}, /* Set LS PLL to quarter rate Disable LS_RX_ENTX to turn off LS transmitter*/{ TLK81_CLK_CONTROL, 0x0080 }, // CLKOUTxP/N disable{ TLK81_HS_ALIGN_CODE_CONTROL, 0x02BC },// Set TX marker selection on lane 0{ TLK81_HS_CH_CONTROL, 0x0880 }, // Enable TX marker replace { TLK81_EXT_ADDRESS_CONTROL, TLK81EXT_VS_TX_MARKER_REPLACE_CHAR },{ TLK81_EXT_ADDRESS_DATA, 0x25C }, // TX replace char 0x25C{ TLK81_EXT_ADDRESS_CONTROL, TLK81EXT_VS_TX_IDLE_P_CHAR },{ TLK81_EXT_ADDRESS_DATA, 0x2FD }, // TX idle Pchar{ TLK81_EXT_ADDRESS_CONTROL, TLK81EXT_VS_TX_IDLE_N_CHAR },{ TLK81_EXT_ADDRESS_DATA, 0x2FD }, // TX idle Nchar{ TLK81_RESET_CONTROL, 0x0008 } // DATAPATH_RESET

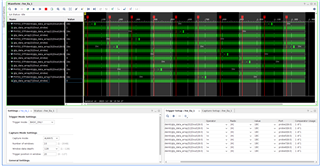

And this is what we get after we perform lane deinterleaving in the FPGA:

We suspect that this happens due to clock tolerance compensation. But then we would expect a single idle character (0xFD). So why is it not a single 0xFD character and why do we get a few 0xFE characters as well?

Thanks in advance.

~Alexander