Hello,

According to datasheet A1 contains internal Pull Down. Is the state of A0 (pin21) defined when left floating please?

BTW: TMDS181 eval board is responding on 5E address when these pins are left floating.

Thank you.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

According to datasheet A1 contains internal Pull Down. Is the state of A0 (pin21) defined when left floating please?

BTW: TMDS181 eval board is responding on 5E address when these pins are left floating.

Thank you.

Hello,

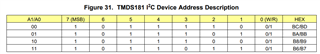

The 7- bit device address for TMDS181 decides by the combination of EQ_SEL/A0 and A1. Figure 31 clarifies the TMDS181 target address.

You are observing the first address line in the Figure 31 when you are using the eval board. A0 is defined as 0.

Thanks,

Zach

Hello,

Thank you for your feedback.

Is the logic state of A0 (pin21) defined when left floating on TMDS181 device please? (I am not able to find that information in specification)

Can TI confirm that when the pin 21 of TMDS181 is left open (NC) then A0 I2C address bit will be always interpreted as logic low by TMDS181 please?

Regards

Hello,

NC cannot guarantee that it will always be interpreted as logic low.

PIN21 is 3 level for pin strap programming but 2 level when I2C address.

Thanks,

Zach