Other Parts Discussed in Thread: TPD1E01B04-Q1

Hi team,

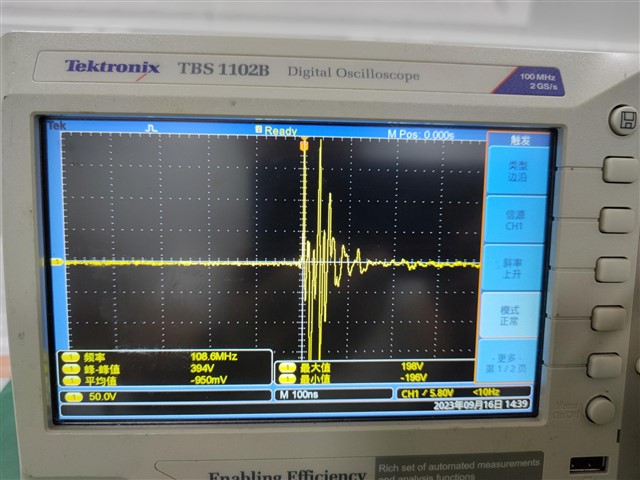

We now have a electrostatic test problem

During the electrostatic test, if the air or contact current is ±4kV or above, video freezes will occur. The test point is any point on the metal shell of the camera. The hardware-related schematic diagram and PCB have been confirmed by other colleagues, and corresponding rectifications have been made, but there is no obvious improvement; In terms of software, the relevant suggestions on E2E have not been significantly improved after adjustments. I will attach the link to the previous e2e later.