Other Parts Discussed in Thread: ALP, DS90UB953-Q1

In our previous generation of the product we design we have used a DS90UB933 serializer for providing the video output data to in-vehicle displays. Since this serializer received parallel data input (using RAW10), the deserializer chips (DS90UB934, DS90UB936) were configured for the FPD-Link III interface using DVP input (RAW10).

We are currently evaluating the possibility to change DS90UB933 to DS90UB953 - this serializer will use MIPI CSI-2 as input but needs to work with DVP mode configured on the FPD-Link III interface. Using two EVKs, DS90UB953 EVM and DS90UB954 EVM, we are trying to configure them to work in DVP mode on the FPD-Link III interface.

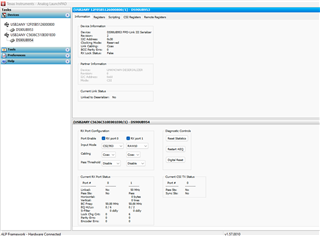

If we change the Input mode for the DS90UB954 deserializer to RAW10 and change the DS90UB953 serializer register 0x03 MODE_SEL to 0x5D (FPD_COAX set, MODE_OV set, MODE set to 101 - DVP External Clock Mode) we are able to see Link status set on the DS90UB954 deserializer while the Link status is unset on the DS90UB953 serializer.

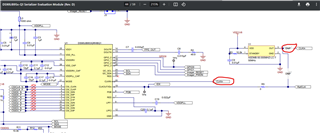

As a prerequisite for the previously described steps, we have connected the output of Y1 (external clock) to the CLKIn trace that leads to the DS90UB953 serializer CLKIN pin.

We are unsure if we need to change other register settings on the serializer or deserializer in order to have a working link between the deserializer and serializer. We require TI support on this topic so please let us know what to change/verify on the serializer or deserializer (registers, EVM updates, etc.).