Other Parts Discussed in Thread: DP83848M,

Hello,

I have some problem with DP83848m/t/H PHY,

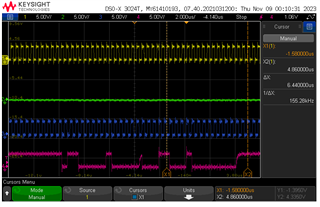

i am usign the devt board : DP83848H-MAU-EK and the communication seems not working

I sent eth packet with FPGA the MII interface seems to be OK, wut nothing on wireshark ....

the communication with MDIO/MDC is OK / read back OK

Is it possible to have the whole registers confiugation needed to configure a MII communication ( by registers and set the jumpers of board...)

Thanks in advance.

DT.