Part Number: DP83826E

Other Parts Discussed in Thread: AM2432

Hi Team,

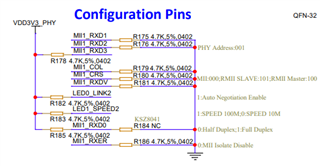

This is customer first design in AM2432+DP83826.

Please help to review the design. Focusing on cheching the interface/config/clock. There are 2 MII network ports and 2RMII slave network ports.