Hi Team,

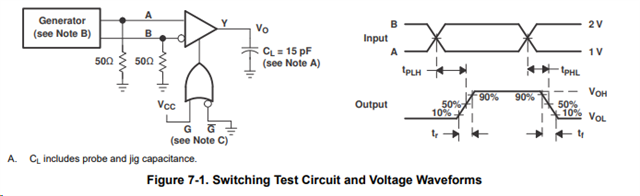

Do we have any data or insight on the propagation delay that this Diff Line Receiver has over temperature, load and process variation?

My customer is trying to get repeatable prop delays, so any insight here is appreciated. They are open to alternative recommendations in the same footprint, if that enables them to have more repeatable prop delay across devices.

Thanks,

JP