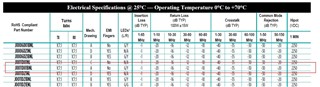

Part Number: DP83822HF

SIr,

I try to make communicate two DP83822, but I always receive 0x5 on rx pins.

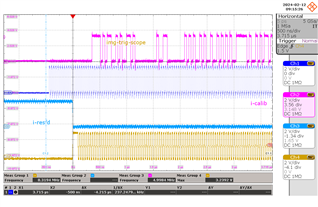

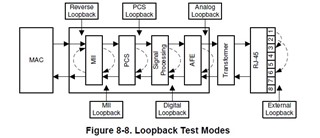

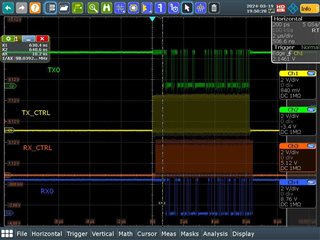

I tried to loopback with MII, and it works, I receive the frame I send (first picture).

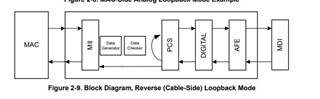

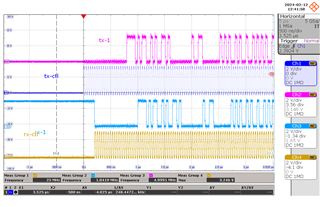

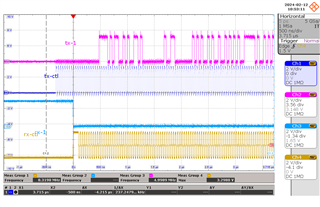

But when I try with pcs loopback, Rx pin are always on 0x5 value with Tx_ER at 1 on the two first nibbles. (second picture). I have the same behavior when I received data from other phy.

I think PCS can't code or decode, but I don't know why.

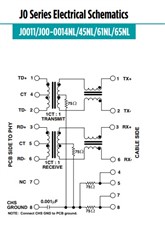

I set this configuration :

Disable_all_IRQ; //Correct Strap pin config //Disable FX, FPGA pin must sink current so strap not read correctly ClearBit(this, CR2, FX_Enable_bit); SetBit(this,BMCR,Speed_Selection_bit); SetBit(this,BMCR,Autoneg_Enable_bit); SetBit(this,BMCR,DuplexMode_bit); SetBit(this, ANAR, Tx_100b_full_bit); //advertise 100Mbps SetBit(this, ANAR, Tx_100b_half_bit); //advertise 100Mbps ClearBit(this, ANAR, TXe_10b_full_bit); ClearBit(this, ANAR, TXe_10b_half_bit); //active rgmii ClearBit(this, RCSR, RMII_Mode_bit); SetBit(this, RCSR, RGMII_Mode_bit); ClearBit(this, RCSR, RMII_Clock_bit); ClearBit(this, LEDCR, LED_0_Polarity_bit); //Enable auto mdi SetBit(this, PHYCR, Enable_AutoMDI_bit); ClearBit(this, PHYCR, Led_CFG_bit); ClearBit(this, MLEDCR, MLED_Pol_bit); SetBit(this, IOCTRL1, 0); //TODO refaire globale ClearBit(this,IOCTRL1,1); ClearBit(this,IOCTRL1,2); ClearBit(this, EEECFG3,EEE_capabilites_bit); ClearBit(this, EEE_ADV, Adv_EEE_100bps_bit); //clear energyefficient ClearBit(this,RXCFG,WoL_Enbale_bit); //disable WoL

here screenshot for MII looppback

here with pcs loopback

I do same things with DP83xx811 and it works fine.

I must miss something and I try many configurations.

Could you give me some tips to try?

Thank you.