Hi team,

The RVC lens uses a 962 deserializer, which requires a FrameSync signal for the lens to produce pictures;

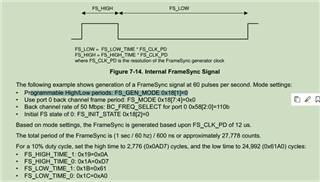

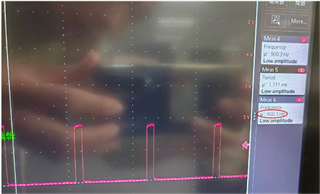

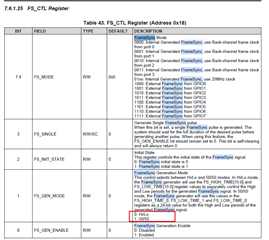

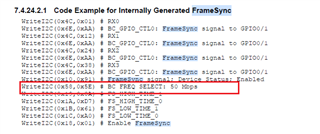

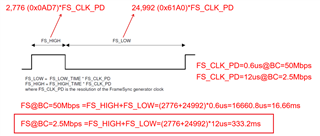

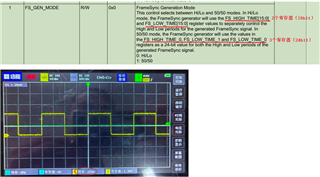

The following is the FrameSync settings in the 962 datasheet. I measured the waveform according to this configuration and found that it was not a 60Hz synchronization signal, but 900Hz;

Question: There should be something wrong with the description in the datasheet. Could you please help confirm the correct setting method (the camera frame rate of the Chase project is 25fps)