Hi,

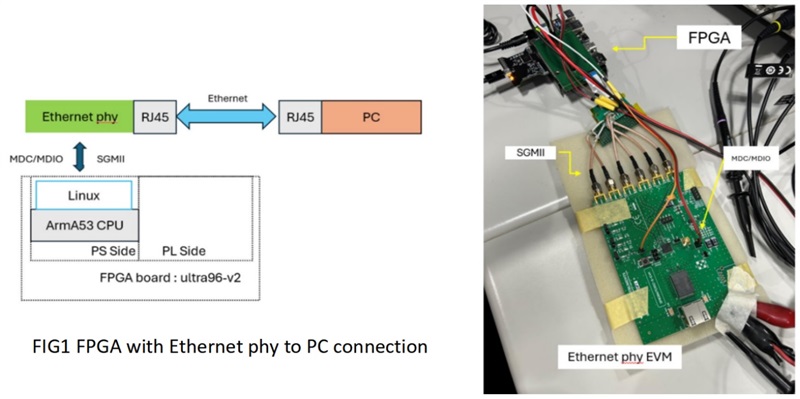

We have DP83867E SGMII EVM communicating with ultra96v2 by SGMII (6 wire), We read registers by mdio interface, but it cannot ping PC.

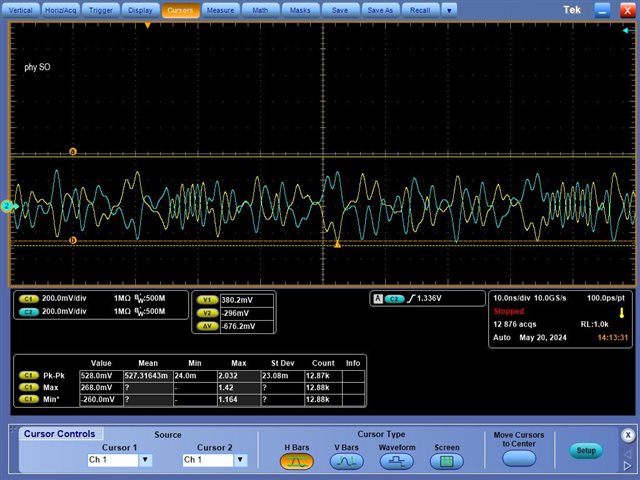

SGMII can no signal.

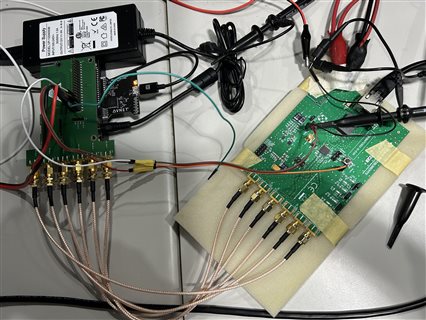

As Fig1. Current use ultra96v2 PS side A53 CPU with Linux and we want to use SGMII mode with TI DP83867E PHY (DP83867E EVM) connection.

The following are confirmed:

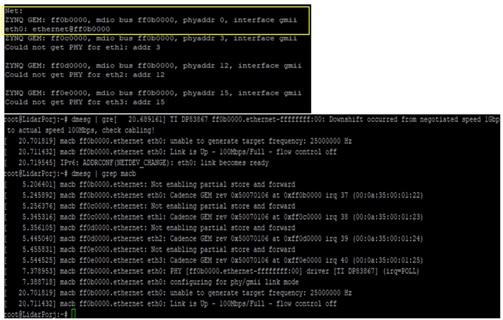

- Linux boot checking:

FPGA FSBL loader can initial ethernet phy(ethernet@ff0b0000),macb drive link up to 100M

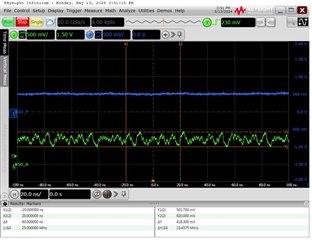

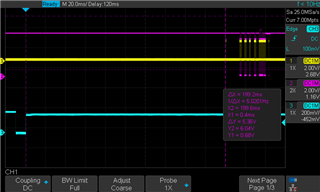

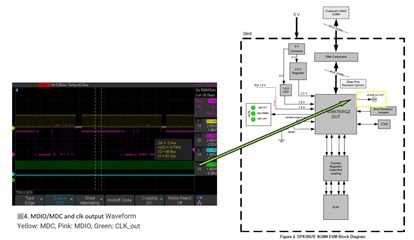

- Check MDIO/MDC and clk output waveform

Yellow: MDC,Pink: MDIO, Green: DP83867E CLK output

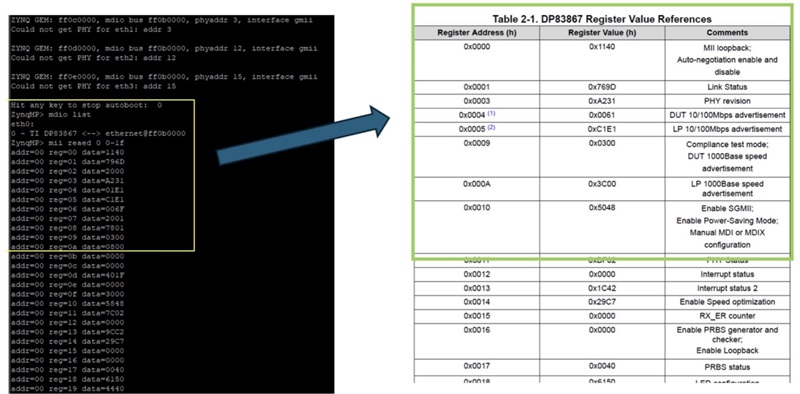

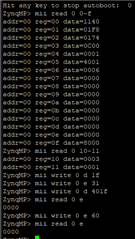

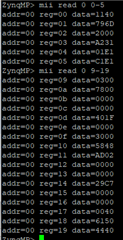

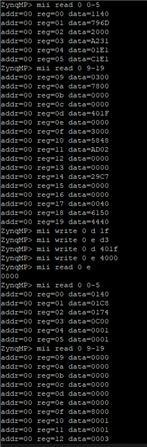

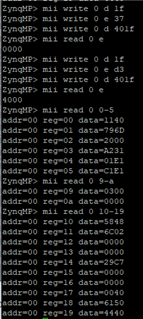

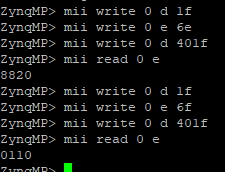

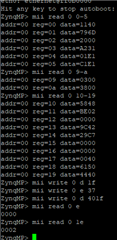

- uboot mii check

here is mii read 0-1f. Some register status I don't know how to solve.

a. BMSR bit2 alway 0 ,How can I solve?

b. d3 set 4000 but read will be 0000. Why can i set SGMII 6 wire mode?

c. CFG4(addr 31 ): 0002