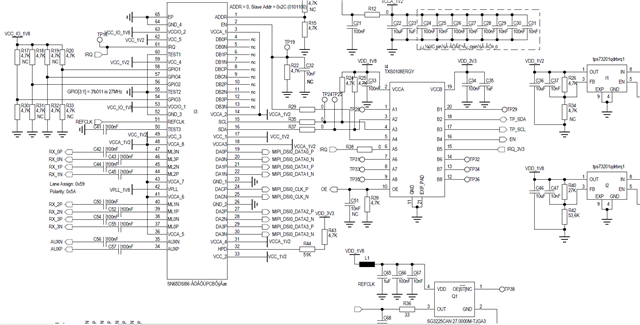

Other Parts Discussed in Thread: SN65DSI86, TEST2

Tool/software:

Hi Ti teams,

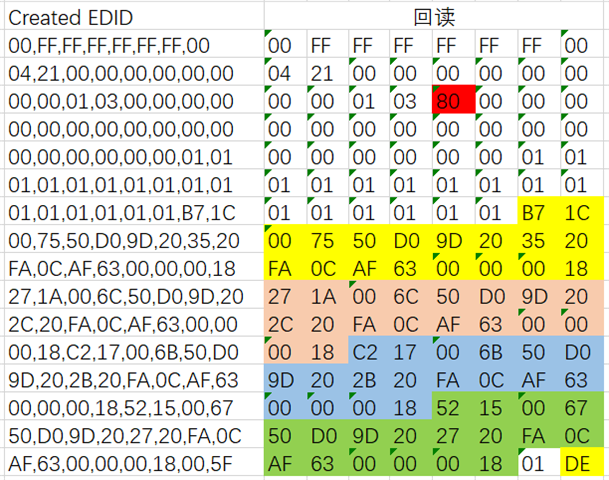

We use SN65DSI86 to display color bar pattern,but only black display. The value of register 0x96 is 0x00, and the value of register 0xF8 is 0x12. The link training is fail.

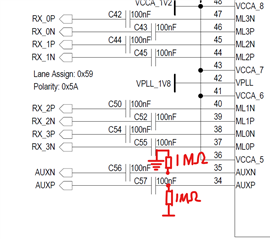

The number of DP lanes we used is 4, and the DP data rate is 1.62Gbps.

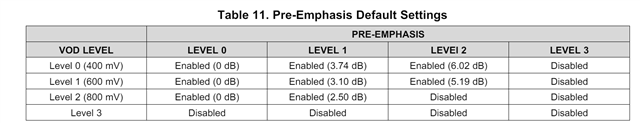

We want to change the Link Training Look-Up-Table default value, could you give me same advice what is the appropriate value.

Best Regards

Emily