Tool/software:

Hello TI Team,

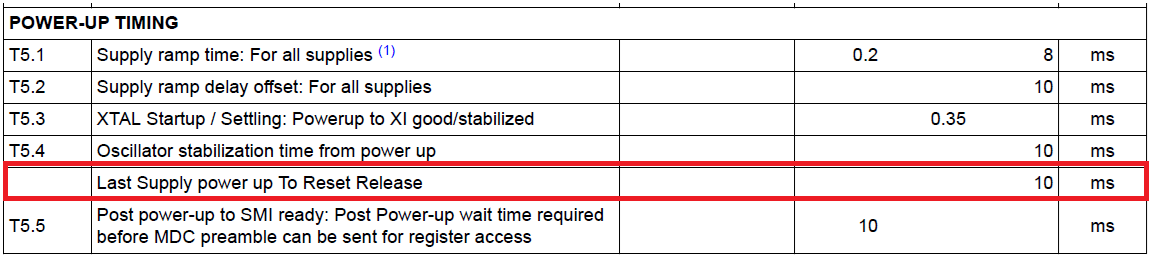

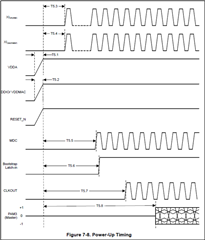

From the datasheet,

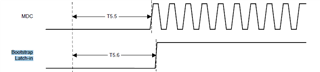

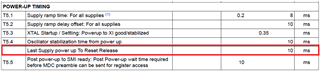

1). T5.1 Supply ramp time: For all supplies

Q: Does VDDIO and VDDMAC also have the same requirement?

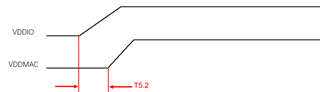

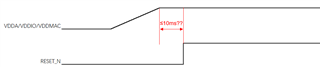

2). T5.2 Supply ramp delay offset: For all supplies

Q: I can't understand this item. It seems same with T5.1 from Figure 7-8. Could you explain more clearly?

Best Regards!