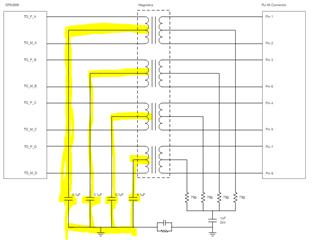

Part Number: DP83869HM

Other Parts Discussed in Thread: DP83869

Tool/software:

Hi Team,

Please help to review the attached schematics for DP83869HM.

Please Note:

1. We are using PHY as Media Converter

2. PHY with SFP & COPPER Interface Schematics is attached.

3. We have 2 PHY ICs, Schematics is the same for PHY2, so only PHY1 schematics are attached.

4. The Power Section is pending I will share it in upcoming threads.

SCH_DP83869_TI.pdf