Other Parts Discussed in Thread: TUSB4020BI

Tool/software:

Hi there

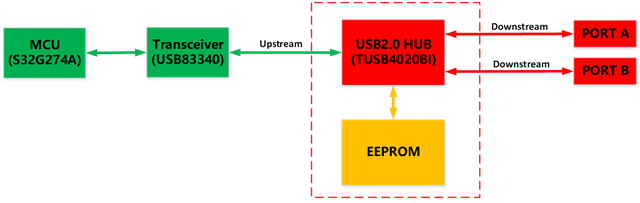

We are currently debugging your company's HUB chip model TUSB4020BI-Q1 based on the NXP S32G274A platform.

We have encountered some issues and would like to consult with you.

The overall system architecture is shown in the following figure.

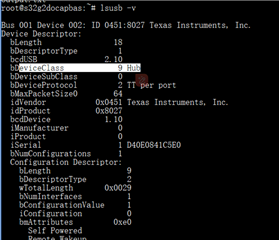

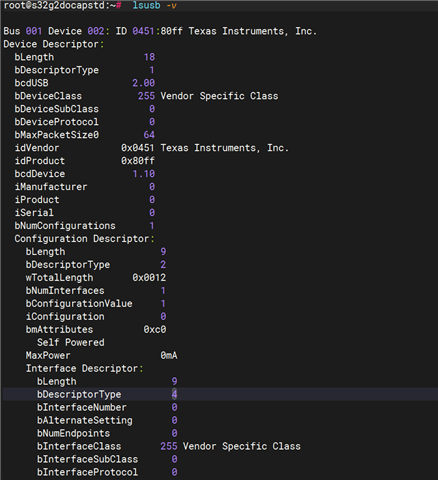

1. Our MCU can recognize the PID and VID of the TUSB4020 chip as the blow image.

Based on this information, we can only temporarily determine that the Upstream Port for MCU and USB communication is communicable; but it is currently uncertain whether the MCU has already connected TUSB4020BI

Identify whether it is a regular USB device or a HUB.

Can you help confirm that the MCU is able to correctly recognize HUB instead of regular USB equipment? If it's not HUB, can you help me see how to adjust it?

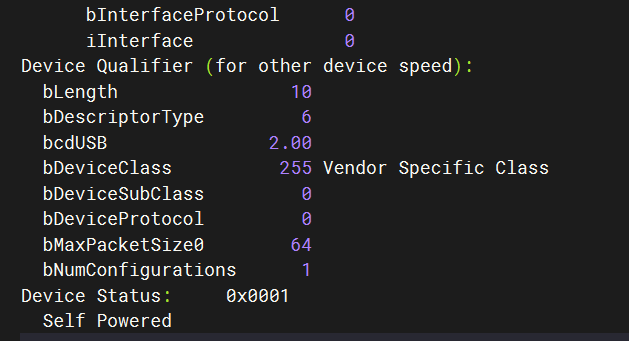

2. Both bDeviceClass and bInterfaceClass are now 255. Is it because our hardware configuration is incorrect, or is it because OTP comes with it? Do we have a way to program and adjust, and do we have tools or methods to configure?(Email:shen.huayi@grce-tech.com)

3. We want to use the Downstream Port to configure OTP and EEPORM (currently the default configuration for power on OTP), but currently the Downstream Port has not been tested. Can you help analyze whether it is a circuit design issue or a configuration issue. If there are relevant upper computer software tools available, can you provide them!(Email:shen.huayi@grce-tech.com)

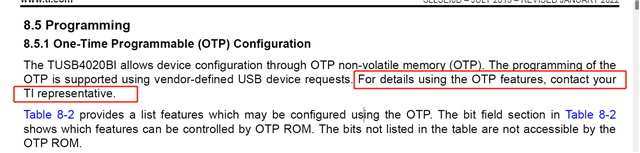

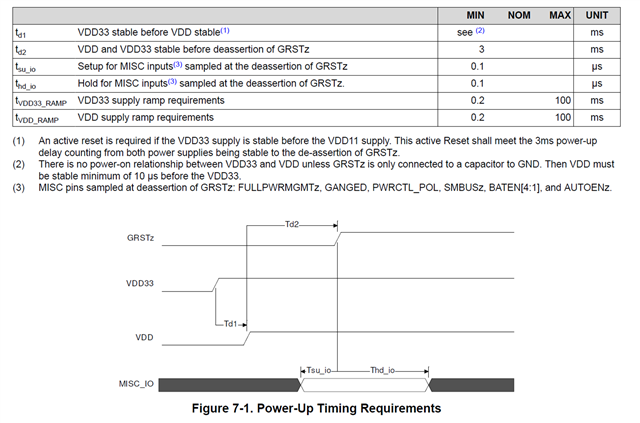

4. Tested the power on timing, with yellow 3.3V, green 1.1V, and blue GRSTZ signals. Currently, the analysis meets the power on timing requirements. Please help to analyze and confirm.

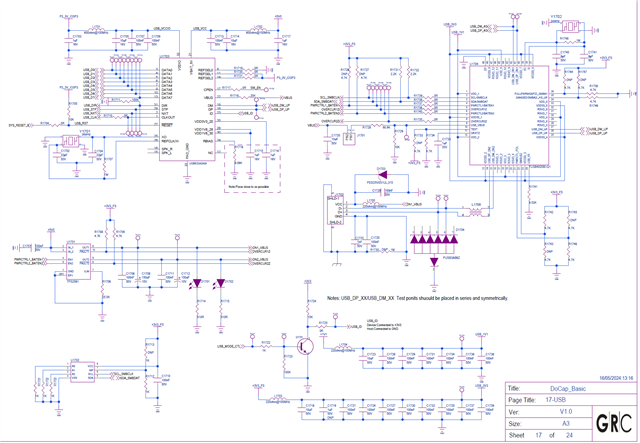

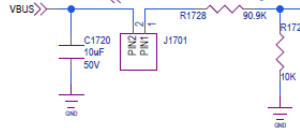

5. Our circuit design is based on your company's demo board as a whole. We have conducted internal verification and have not found any obvious unreasonable areas. Please help to verify and confirm (our schematic diagram is shown in the following figure).