Other Parts Discussed in Thread: DS90UB948-Q1

Tool/software:

Hello TI,

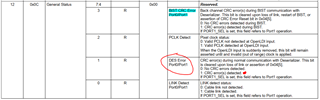

I'm having a project use ds90ub947-q1 and ds90ub948-q1 (FPDLinkIII Serializer and Deserializer). Our system operated quite normally, UI is also displayed on monitor. Just there is a problem that when I read register 0x0C of 947, it's value is 0x07, it's mean that bit1 is set to 1 --> CRC error(s) detected. This is abnormal, right? And what factors could cause this?

Hope receive help soon!