Other Parts Discussed in Thread: AM3358,

Tool/software:

Hi,

We use the DP83822I for the Ethernet transceiver in our AM3358 board, and now, we find our mass product have the below issue for some board:

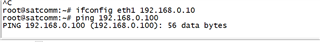

1. The network cards can be correctly recognized, but only eth0 is normal, eth1 cannot ping, and there is no network available, for this case, we can reboot or reset the uboot when we don't turn off the power

that the ethernet signal will normal;

2. Similar as item#1, we reboot or reset the uboot but the ethernet signal is also abnormal;

3. Both eth1 and eth0 can be recognized normally, and the network is also normal. However, after repeated power on and power off tests, eth0 cannot be recognized, and the eth0 RJ45 light doesn't light up;

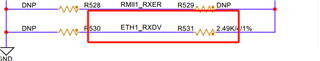

We have no idea how to solve the issue, and please kindly review below schematic diagram and provide your commend that how to check the HW or SW design, and we can solve the issue;

BTW, this issue don't happen in every board, it maybe about 2%-5% probability in our mass product, it is very serious impact on production efficiency, thanks.