Tool/software:

Hi team

Our development product use DS280DF810 for Ethernet Switch. DS280DF810 is place between optical transceiver and SWLSI for 25G transmission.

We have questions about EOM monitor of DS280DF810.

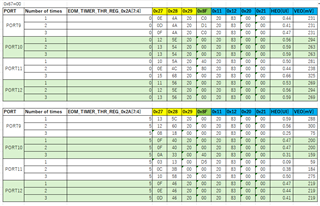

When we repeatedly execute optical signal ON/OFF to the optical transceiver, the EOM monitor value may occasionally become 0 (channel register address 27, address 28).

No matter how many times we read the address, the value remains 0.

At that time, a communication error or link down occur.

Our experiments have shown that the probability that the EOM monitor value becomes 0 depends on the EOM time.

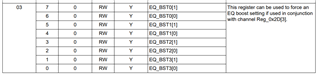

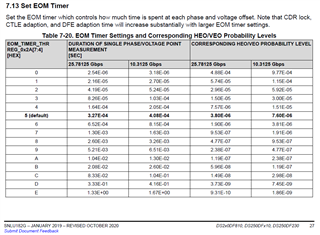

Currently, we use default value of EOM_TIMER_THR REG_0x2A[7:4]=5. In this case we can see that the EOM monitor value becomes 0.

However, as decreasing the value, the probability of the value becoming 0 decreases, and as increasing the value, the probability of the value becoming 0 increases.

Also, changing a register (channel register address 67) to 0(disable), the probability of the value becoming 0 increases.

Can you please tell us what you think could be the reason for this result ?

Are there any side effects of using EOM_TIMER_THR REG_0x2A[7:4] with a register value of 0?

Thanks,

K. Mizobuchi