Part Number: DS90UB927Q-Q1

Tool/software:

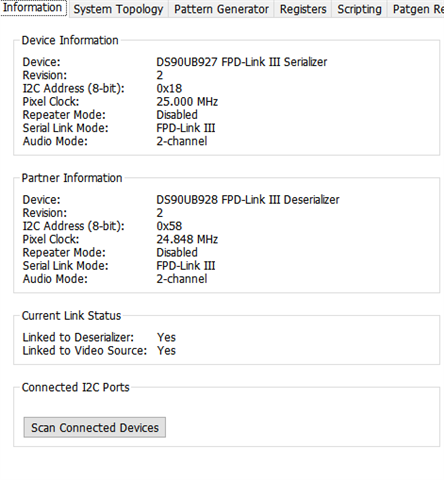

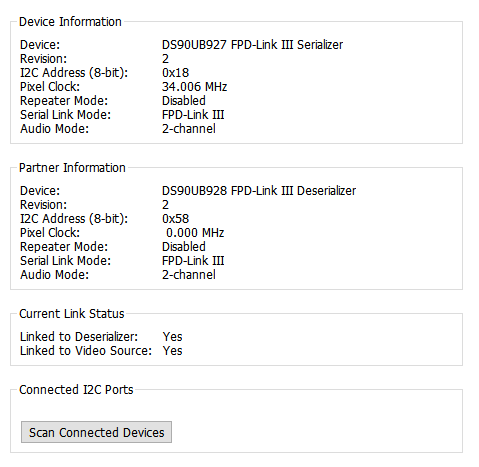

i am use 927 and 928 to send lvds single . i use video source pixclk is 26.2MHz . But in anlog launchPAD pixclk is 33-36MHz instability. 2 picture is use PG Timing Source = internal and interal w/ext.clock. use ext clock pixclk is not correct . I measure pixclk is 26.2Mhz by oscillograph. what can i do next ? please help me! thanks.