Other Parts Discussed in Thread: TDP0604, TMDS181, , TDP1204

Tool/software:

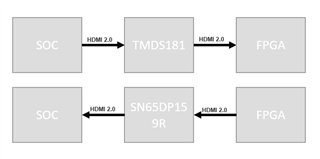

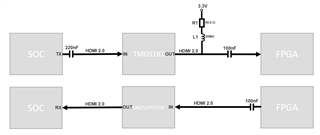

Hi, please kindy help to check SN65DP159RGZT & TMDS181IRGZT SCH below.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

The termination network used to AC couple the HDMI outputs of the TMDS181 will result in an output swing that is cut in half. I recommend using the TDP0604 rather than the TMDS181 as the TDP0604 can receive DC coupled HDMI and internally bias for AC coupled HDMI output. This will improve signal integrity.

Are you able to swap the chip? Do you need a retimer in this application, or will a redriver suffice?

It seems AC coupling is required for the FPGA, so why is there no AC coupling for the DP159?

Hi ,

FPGA's GT transmitter/reciever does not support TMDS Level Signaling and need to use a re-timer to be compliant with TMDS specifications. So, I pick SN65DP159 and TMDS181 by following FPGA board design guide's recommendation.

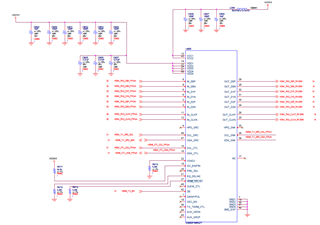

Please kindly see the diagram updated below. BTW, I am not sure if R1 and L1 and 100nF is needed at TMDS181 output side. I just refer to the FPGA reference SCH.

Hi

If SoC TX requires to be AC coupled, then you has to use DP159 as TMDS181 can not support AC coupled input.

Is the SoC RX require to be AC or DC coupled?

Thanks

David

Hi David,

According to your suggestion, I should change TMDS181 to DP159, correct ?

SOC RX don't required to be AC/DC coupled.

Hi,

Correct, because SoC TX is AC coupled, so the DP159 will be the right choice.

Thanks

David

Hi David,

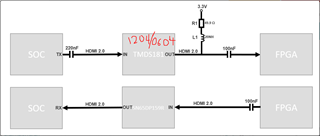

Would you help to check the SCH below. I change TMDS181 to DP159. Let me know if any concerns.

Hi,

Here are the schematic reviews

SN65DP159_Schematic_Review_NXVI_TheiaT1LITE_U4004(11_19_2024).pdf

SN65DP159_Schematic_Review_NXVI_TheiaT1LITE_U4005(11_19_2024).pdf

Additionally for U4004:

Will need pull up to 3.3V for valid DC coupled HDMI detection. After pullup AC cap will be required to AC couple signal. This will effectively cut the output signal swing in half. You will need to maximize swing from the SOC to compensate fro this. Another option is to use the TDP0604(6Gbps) or TDP1204(12Gbps) that can take and AC coupled signal and output an AC coupled output signal. This removes the need to external biasing on the HDMI lines.

Does SDA and SCL not go to the SoC? What is U17E

Additionally for U4005:

Is it ok to have DC coupled HDMI going to RK3588 SoC?

Does SDA and SCL not go to the SoC? What is U17E

Hi Vishesh Pithadiya,

For U4004, HPD_SRC ; SCL_SRC/SDA_SRC ; SCL_CTL/SDA_CTL will connect to RK3588 SOC(U1000) . U17E is Xilinx FPGA.

For U4005, RK3588 HDMI TX need to work at AC coupled mode for HDMI 2.0. But U4005 input is from FPGA and output to RK3588.

BTW, does U4004 and U4005 both sugget to swap to TDP0604/TDP1204 ?

Hi,

For U4004 I recommend swapping over to TDP0604.

For U4005 make sure that the SOC is able to handle DC coupled HDMI. If the SOC is not able to handle DC coupled HDMI, I recommend swapping U4005 to TDP0604 as well.

Keep in mind that the TDP0604/ TDP1204 is a redriver not a retimer. This means that there will be no jitter cleanup. This means that the layout requirements will be more stringent. We are more than willing to have a look at you layout and review it before the board goes into production.

Hi Vishesh Pithadiya,

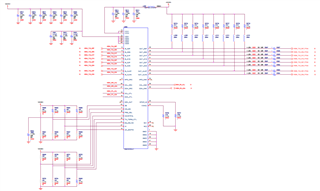

Thanks for your suggestion. I had change U4004 to TDP0604. Would you help to check if any concerns? Thanks.

For U4005. I would keep DP159 as previous. After checked with SOC vendor, DC coupled is supported at HDMI_RX. It's should be no risk.HDMI_Retimer_20241121.pdf

Hi Vishesh Pithadiya,

After internal discussed, I will change U4005 to TDP0604 for better BOM control. Please hold the SCH review. I will update the SCH later.

Hi Vishesh Pithadiya,

Please kindy refer to the update SCH below.

BTW, may I have your suggestion that EQ,TXPRE,TXSWG setting should set to which level in default ?

Hi,

I recommend using I2C as the way to configure the device as this will make tuning easier. Do you have a loss profile for your system?

Typically in a source application the EQ will be a set value to account for the loss of the trace from source to connector. The TXpre will be at no pre-emphasis, and the Vswing will be set to max.

In a sink application the EQ will be calibrated to account for the loss of cable used. The TX pre and Vswing will be tuned for the path from the 0604 to the sink.

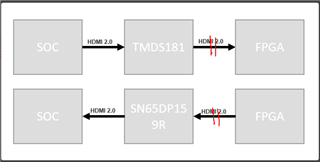

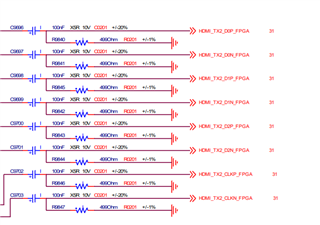

These terminations no longer needed for TDP0604, this is handled internally now.

Please change this. Other than this change most of the schematic looks ok.

Please follow up with a layout when its done. We will help review the layout as well to mitigate risk.

Hi Vishesh Pithadiya,

I am not quite sure what is "system loss profile". Could you be more specific? Do you mean that to get PCB simulated from the lab (PCB signal integrity/Quality)?

So, EQ should set to a value (may need to refer to the simulation result?) TXPRE set to 0dB ; TXSWG set to +5% for HDMI2.0,HDMI1.4 set to 10% as default, correct ?

Hi Vishesh Pithadiya,

Noted, I would delete the caps and the 499 ohm. Thank you.

One question here, should I create another task for the layout review or I could simply post it here when the layout is ready? Please advise.

Hi Vishesh Pithadiya,

I am not quite sure what is "system loss profile". Do you mean that to get PCB simulated from the lab (PCB signal integrity/Quality)?

As in current design, EQ should set to a value (may need to refer to the simulation result?) TXPRE set to 0dB ; TXSWG set to +5% for HDMI2.0,HDMI1.4 set to 10% as default, correct ?

By system loss profile, I mean that we need to look at the signal path and find the total loss in dB.

Its recommended to place the redriver at a point in the PCB where approx 75% of the max RX equalization(dB) will be used. The input trace/cable will have a loss associated with it. We will se the EQ of the TDP0604 to account for this loss.