Tool/software:

Hello,

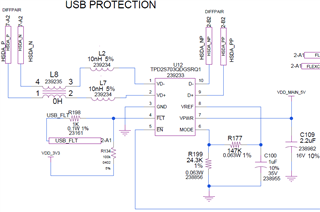

We have the TPD2S703QDGSRQ1 in a released product, recently we're experiencing some issues with some boards.

Initially it was a very small number, but now we're noticing more failures where we losing communication at high speed.

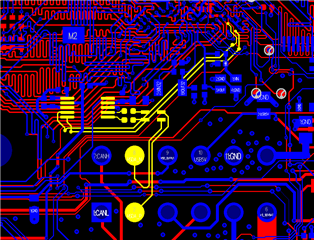

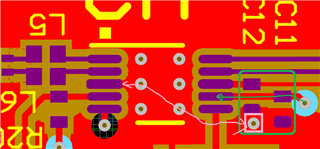

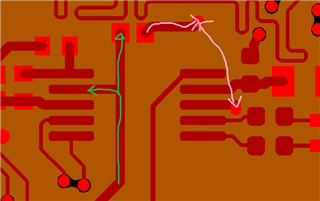

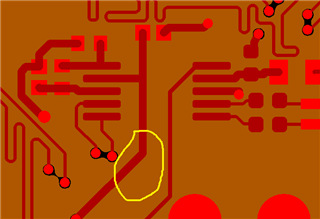

Based on the above design, in a working circuit, Vmode =. 5V and Vref = 3.5V,

In a malfunction circuit, Vmode .64V and Vref = 4.57V.

Can you provide your expert advice on what would cause Vref to jump to 4.57V?

Thank you,

Tony