Part Number: DP83867IS

Tool/software:

Hi Team,

Communication problem occurs with a specific link partner.

In link-up process of once in 200, Ping does not work.

Based on the register information, we believe that the cause is a Master/Slave mismatch under the auto-negotiation process.

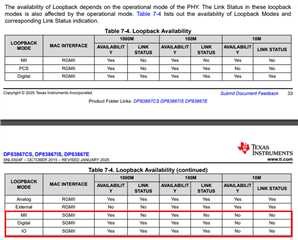

Is loopback function effective in identifying the cause of the Master/Slave mismatch?

I have asked several questions about this issue, but it has not yet been resolved.

We must resolve this issue early.

DP83867IS: Communication problems

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1447700/dp83867is-communication-problems

DP83867IS: About IDLE ERROR COUNTER in register 0x000A bit[7:0].

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1448230/dp83867is-about-idle-error-counter-in-register-0x000a-bit-7-0

Best Regards,