- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

Tool/software:

Dear Receiver,

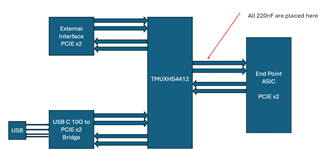

We have a setup as shown below

Kindly help me answering below queries.

01. Is the AC cap placement correct?

02. The impedance 85Ohms supported for all the ports?

Kindly request you to write back as soon as possible. we are moving to Tape out phase soon.

Regards,

Sayeed Khan

Hi Sayeed,

01. Is the AC cap placement correct?

This block diagram makes it hard to tell where the AC cap is being placed. Typically, 220nF AC caps should be placed on the TX lines of the PCIE lanes. I believe the red line is pointing towards an RX line, which should already have 220nF caps on the line downstream, closer to the external interface or the USB-C Bridge.

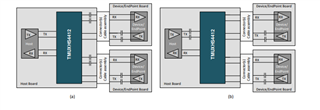

The lines coming out of the End point ASIC are TX lines I'm assuming, and those should have 220nF caps on them for AC coupling. The picture below is a good picture of how AC caps are recommended to be placed:

02. The impedance 85Ohms supported for all the ports?

Yes, 85Ohm differential impedance should be supported by this device.

Please let me know if you have any other questions.

Thanks,

Ryan

Dear Ryan,

Thanks for replying at your earliest.

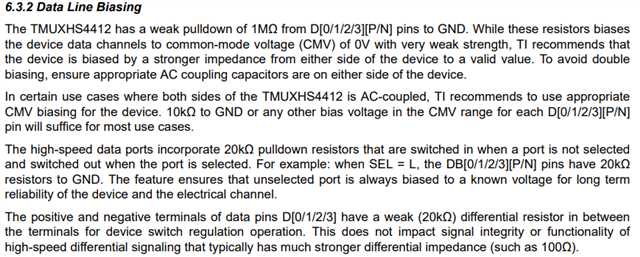

From the Block Diagram, we have two Root options to a single End point

1. External PCIE x2 (CFX). We have not used any ac caps on these lines in our previous designs.

2. USB 10G to PCIE x2 (On board), here we are required to have TX AC Caps as well as RX AC Caps.

Currently, I have put all the AC Caps on the COM side of the TMUXHS i.e Port DxP/N. Kindly let me know, if this approach should be fine ??

Regards,

Sayeed Khan.

Hi Sayeed,

In my opinion, it is better to have the TX AC caps here. Plus, the common-mode voltages of these signals need to be supported by this device.

Its my understanding that typically, PCIE does need AC caps, at least on the TX lines.

Additionally, if RX AC caps are needed on the USB lines, it is recommended that these capacitors be 330nF, and on the same side as the TX capacitors.

Please let me know if you have any other questions.

Thanks,

Ryan

Dear Ryan,

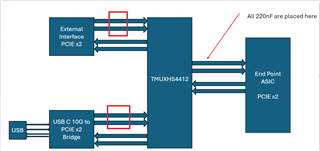

I have updated the Block Diagram

Kindly note

Moving forward, END Point ASIC shall be Device, Option 1 & 2 will be HOST 1 and Host 2 respectively,

HOST 1 : External

HOST 2 & DEVICE on the same PCB.

1. When Device was directly connected to HOST1, we have not provided AC Caps on Device TX, as it has internal AC caps on the TX Lanes, for Device RX Relied on HOST1 AC Caps.

2. In this case, Since HOST 2 in on the same PCB as Device, can we only put to HOST 2 TX lanes??

3. About CMV, would you please elaborate on what parameters do I need check for HOST 2 exactly to understand and implement.

Thanks,

Sayeed Khan

1. When Device was directly connected to HOST1, we have not provided AC Caps on Device TX, as it has internal AC caps on the TX Lanes, for Device RX Relied on HOST1 AC Caps.

Got it, if HOST1 TX AC caps and Device TX caps are both 220nF, then I believe this should be okay.

2. In this case, Since HOST 2 in on the same PCB as Device, can we only put to HOST 2 TX lanes??

For HOST2 to Device and Device to HOST2, 220nF caps are needed on the TX lines.

RX capacitors (330nF) are not typically required in both the cases of HOST1 or HOST2. For both cases, you can just have caps on the TX lines of 220nF. Even if these devices are on the same board, there should be caps on the TX lines of the HOST and device.

3. About CMV, would you please elaborate on what parameters do I need check for HOST 2 exactly to understand and implement.

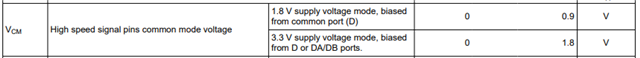

The main thing to ensure is that the Common-mode voltage of the signal you are using is supported by the mux:

Depending on the supply voltage being provided to the mux, as long as the VCM is within the range recommended by the datasheet, the signal should be within an acceptable range to be muxed.

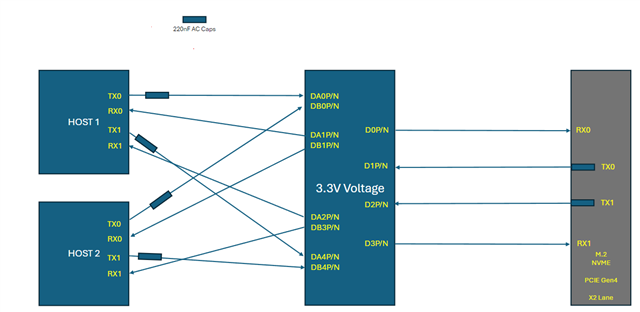

If these signals are not within an acceptable range, they will need to be biased down using an external resistor:

Please let me know if you have any other questions.

Thanks,

Ryan

Dear Ryan,

1. Do you have any reference for us to share with for CMV understanding. Does it require for PCIE GEN3 and GEN4 HOST / END if are compliant to PCIE base spec 3.0 and 4.0??

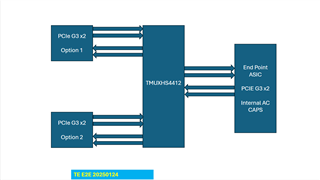

2. Please find below reference of our complete implementation of 2Host 1Device configuration

3. In PCIE Gen4 compliance with TMUXHS4412, have they used CMV biasing.??

4. Kindly share any reference / working example for PCIE GEN4 implementation. We have a very tight real estate on our board and I am completely in dilemma on the CMV.

I share my sincere regards for your help on this.

With Regards,

Sayeed Khan

Hi Sayeed,

1. Do you have any reference for us to share with for CMV understanding. Does it require for PCIE GEN3 and GEN4 HOST / END if are compliant to PCIE base spec 3.0 and 4.0??

As long as the voltage levels for PCIE Gen3 and Gen4 are within the levels listed in the datasheet, I don't believe you will need to worry about biasing as long as the mux is being used at Vcc = 3.3V. This device was rated for PCIe 3 and 4.

This FAQ provides a better explanation for coupling and VCM: https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1342811/faq-tmuxhs4212-when-and-how-to-ac-coupling-the-passive-mux?tisearch=e2e-sitesearch&keymatch=tmuxhs4412#

2. Please find below reference of our complete implementation of 2Host 1Device configuration

I don't believe I see any issues with this implementation

3. In PCIE Gen4 compliance with TMUXHS4412, have they used CMV biasing.??

This document reports our testing process for PCIE Gen4 compliance testing. It should mention or indicate if any CMV biasing was needed: https://www.ti.com/lit/ug/slat159/slat159.pdf

4. Kindly share any reference / working example for PCIE GEN4 implementation. We have a very tight real estate on our board and I am completely in dilemma on the CMV.

The report should show the board that we used for testing. If you want, I can send the design files for the board over to you to look at.

Thanks,

Ryan

Dear Ryan,

1. Kindly request you to share the files you have tipped at last.

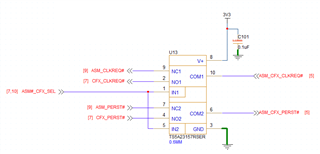

2. I have used below implementation for CLKREQ and PEREST MUX.

Kindly share your thoughts on this one as well.

With Regards,

Sayeed Khan

Hi Sayeed,

Please accept my E2E friend request, and I will PM those files over to you.

2. I have used below implementation for CLKREQ and PEREST MUX.

I can't say I've ever used this switch before. From what I can tell looking at it, I believe this is setup correctly, yes.

The other recommendation I would have for 2:1 muxing, which I think you are looking to do, is the TS3USB221.However, if this switch works for you in terms of voltage and bandwidth, then I believe it should be fine.

Thanks,

Ryan

Dear Ryan,

1. Please find the comments shared from our end customer on this, Please let us know if they align with your opinion on VCM.

2. Thanks for sharing your friend request. Kindly share the mentioned design files.

3. My HOST1 is PCIE Edge Finger & HOST 2 is on board chip. I just had a PCIe Guidelines watched from TI on Youtube to have 85E for CEM / Edge Finger and 100E for same PCB HOST. Do I differently connect them / Use 85E for both the HOSTs.

Thanks,

Sayeed Khan

Hi Sayeed,

1. Please find the comments shared from our end customer on this, Please let us know if they align with your opinion on VCM.

Makes sense to me, I have no issue with it.

2. Thanks for sharing your friend request. Kindly share the mentioned design files.

Responded over E2E PM.

3. My HOST1 is PCIE Edge Finger & HOST 2 is on board chip. I just had a PCIe Guidelines watched from TI on Youtube to have 85E for CEM / Edge Finger and 100E for same PCB HOST. Do I differently connect them / Use 85E for both the HOSTs.

It is better to have the same impedance across the entire system, which ever one is closest to being within compliant spec for PCIE differential impedance. Switching between different impedances in the trace or at the mux will only cause reflections in the signal.

Please let me know if you have any other questions.

Thanks,

Ryan

Dear Ryan,

Do I need to worry about the below remarks.

I can use the whole of MUX and have complete throughput, Right?

Thanks,

Sayeed Khan

Hi Sayeed,

This is only referring to the EVM, which didn't use all the pins on the device as the size of the EVM was too small. It should have no issue for your setup.

Thanks,

Ryan

Dear Ryan,

1. For USB3.2 10G x2 lane, We have to only match the intra pair skew to <5Mils Right? Inter pair skew is not mandatory, right?

2. Same guidelines for PCIE x2 as well?

3. TMUXHS4412 RSVD42, I left floating, is it fine?

4. As per DS 7.4, Pulling PD low after sustained power supply is recommended along with an ample capacitor. I have hard pulled to GND via 10K. EVM also, no such provision??

With Regards,

Sayeed Khan

Hi Sayeed,

1. For USB3.2 10G x2 lane, We have to only match the intra pair skew to <5Mils Right? Inter pair skew is not mandatory, right?

2. Same guidelines for PCIE x2 as well?

The recommendation for both specs with intra-pair skew is <5 mils, correct. We do not have a requirement for inter-pair skew.

3. TMUXHS4412 RSVD42, I left floating, is it fine?

This should be pulled down to ground with a 4.7KOhm resistor. It cannot be left floating.

4. As per DS 7.4, Pulling PD low after sustained power supply is recommended along with an ample capacitor. I have hard pulled to GND via 10K. EVM also, no such provision??

If possible, I would recommend driving the PD pin to only pull low when VCC is stable, rather than having it permanently pulled down.

Thanks,

Ryan

Dear Ryan,

Shall I use a CR circuit for this PD application. I will pull up the PD with Capacitor and pull down with 2.2K. The moment Supply comes, PD will be 3.3V, then it goes down to zero and remain zero.

Thanks,

Sayeed Khan

Hi Sayeed,

I believe you can likely go ahead and just do a 10KOhm pull down for the PD pin, as is done on the EVM. You shouldn't need to use a CR circuit for this implementation. The controller option/driving it externally was just a recommendation in case it was possible.

Thanks,

Ryan