Hi,

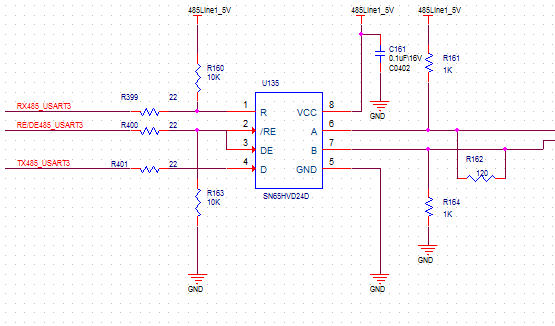

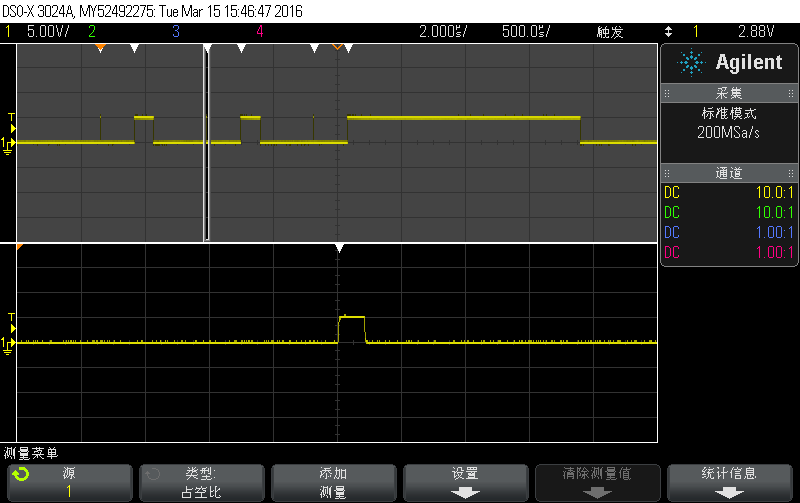

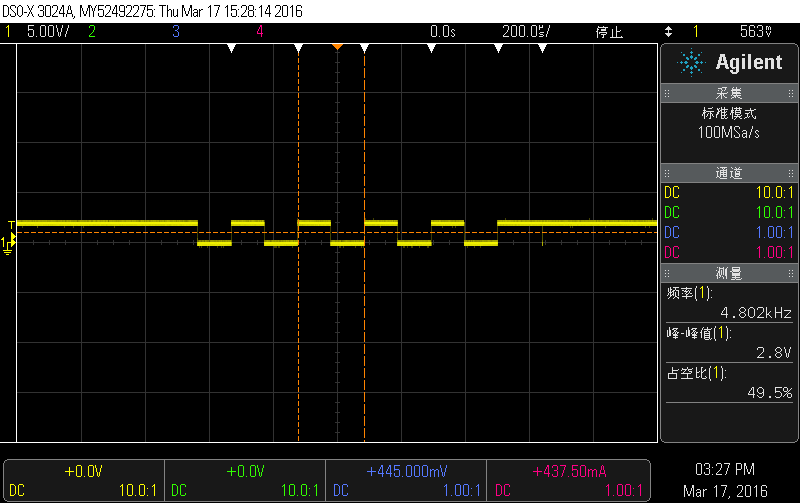

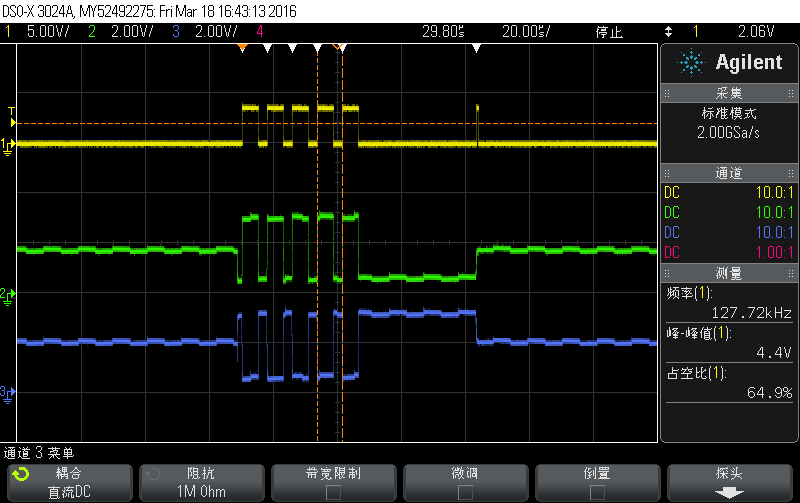

when I use SN65HVD24 to act as a receiver,it has a pulse on R pin about 0.8us before the valid data. The next scope is 2400bps.when I use 9600bps, all valid data become zero level.Is the circuIt's schematics right?What is the problem?

Thanks a lot.