Hi,

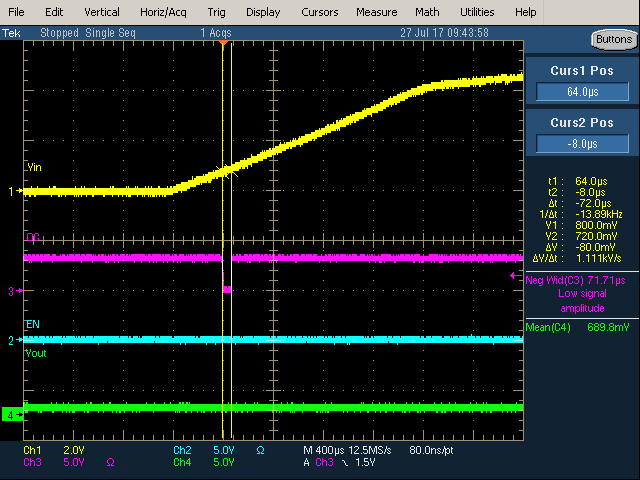

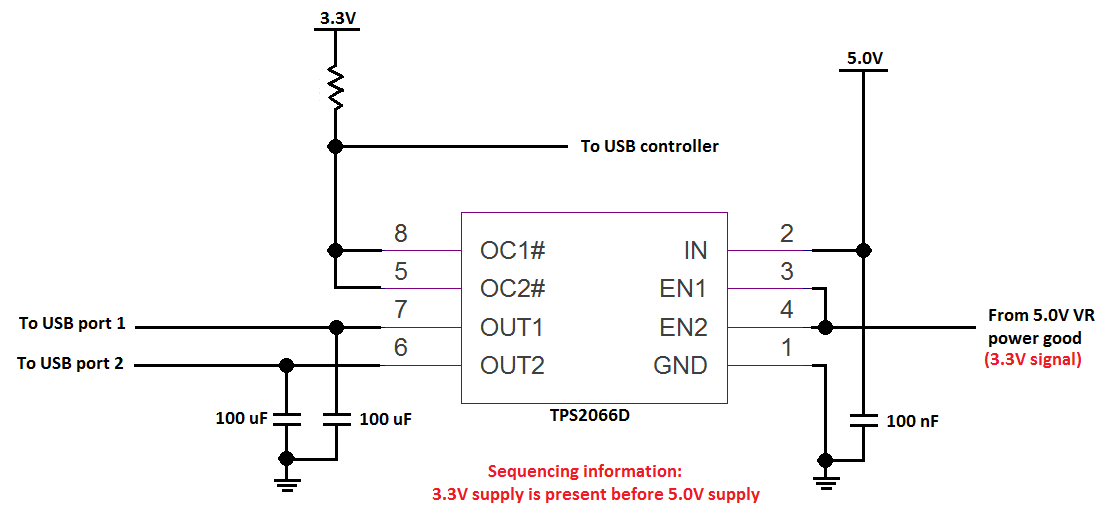

We are currently using the TPS2066D as load switch for USB ports. y at the VIN pin ramps up, a glitch occurs on the OC# pin while VIN is still very low (~ 0.72V). This glitch is sometimes interpreted as an overcurrent event by the USB controller and causes port malfunction. There is nothing else connected on the line between the switch and the controller, so this glitch must be issued by the TPS2066D itself.

I would like to know if this is an expected behavior for this component. I know there is an UVLO feature that should prevent malfunction while VIN supply is below a certain range, but in our case this feature does not seem to prevent the OC pin from glitching.

See attached scope capture.

Thank you.

Cedrick